概述

MIPI® SPMIsm 验证 IP,用于您的 IP、系统级芯片和系统级设计测试。

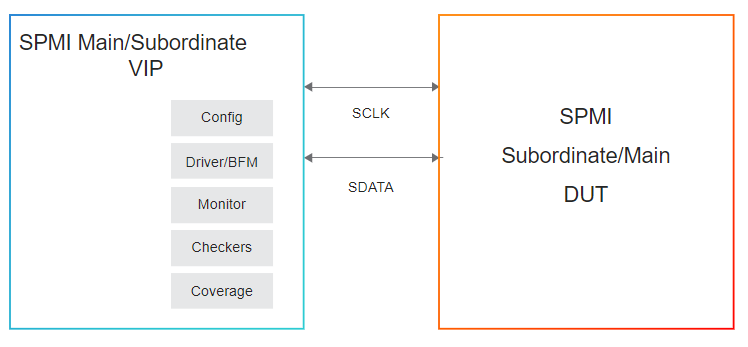

Cadence 为 MIPI® SPMIsm(系统电源管理接口)协议提供了一个成熟而全面的验证 IP (VIP)。Cadence® SPMI 验证 IP 整合了最新的协议更新,提供了完整的总线功能模型 (BFM),并集成了自动协议检查和覆盖率模型。SPMI VIP 可以轻松集成在 IP、系统级芯片 (SoC) 和系统层面的仿真平台中,帮助您减少测试时间,加速验证收敛,并确保最终产品的质量。该 VIP 可在所有主流的仿真器上运行,支持 SystemVerilog 语言,以及相关的方法学,包括通用验证方法学 (UVM) 和开放验证方法学 (OVM)。

支持的规范:面向 SPMI v1.0 和 v2.0 的 MIPI 规范。

产品优势

主要功能

下表列出了 VIP 中实现的规范的一些重要功能:

功能名称 |

描述 |

|---|---|

拓扑结构 |

|

时钟 |

|

主连接 |

|

主仲裁 |

|

从属类型 |

|

SHOW ALL

5 of 13

仿真测试集合

具有覆盖模型的综合测试集合,可实现简单快速的设计和初始环境搭建(bring-up)。

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles