概述

Flash Toggle NAND 存储器设备的黄金标准,面向您的 IP、系统级芯片和系统级设计验证

自 2011 年起投入生产,应用于诸多生产设计。

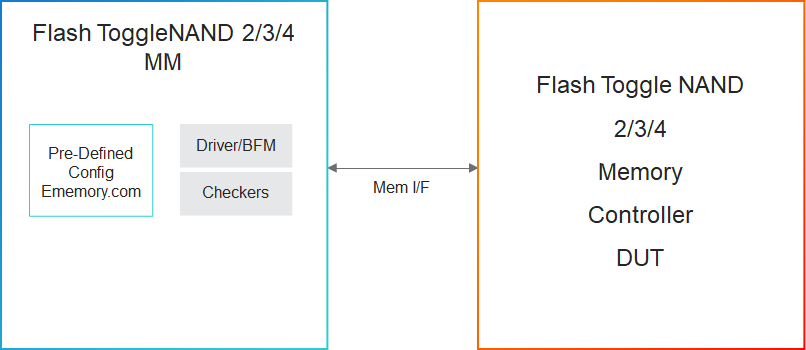

面向 Toggle NAND 的 Cadence® 验证 IP (VIP) 适用于知识产权 (IP)、系统级芯片 (SoC) 和系统级验证,为使用 toggle 模式的 DDR 2.0 及以上版本提供 Flash NAND 设备验证。面向 Toggle NAND 的 VIP 与行业标准的通用验证方法 (UVM) 兼容,可在所有领先的仿真器上运行,并利用行业标准的 Cadence 内存模型核心架构、接口和使用模型。

支持的规范:海力士、三星、东芝和闪迪的 Toggle NAND DDR 2.0 Single-Level-Cell (SLC) 和 Multi-Level-Cell (MLC) 设备,以及 Toggle NAND DDR 3.0/4.0Single-Level-Cell (SLC)、Multi-Level-Cell 和 Triple-Level-Cell (TLC) 设备。

产品优势

主要功能

下表列出了 VIP 中实现的规范的一些重要功能:

功能名称 |

描述 |

|---|---|

速度 |

|

每单元比特数 |

|

内存大小 |

|

配置能力 |

|

SHOW ALL

4 of 9

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles