Overview

Gold standard for JEDEC® ONFI memory device for your IP, SoC, and system-level design verification.

In production since 2011 for dozens of production designs.

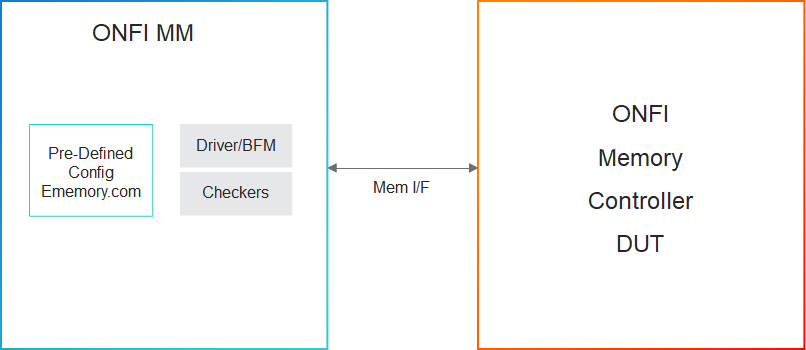

The Cadence® Memory Model Verification IP (VIP) for ONFi is the verification solution for NAND flash memory interface based on any version of the Open NAND Flash interface. The VIP supports all the interfaces: SDR, NV-DDR, NV-DDR2, NV-DDR3, and NV-LPDDR4, as defined in the standard. The interface mode can be dynamically switched from one to another during the simulation till NV-DDR2. Through the "Volume Address" feature, defined in the latest standard, any number of device models can be connected to a single "chip enable" signal to allow testing of CE_n pin reduction scenarios.

Supported specification: JEDEC ONFi versions 1.0, 2.0, 3.0, 4.0, 4.1, 4.2, 5.0, 5.1

Product Highlights

Key Features

The following table describes key features from the specifications that are implemented in the VIP:

Feature Name |

Description |

|---|---|

Speed |

|

Interfaces |

|

General Functionality |

|

Core and Bus timing |

|

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles