概述

HyperRam 存储器设备的黄金标准,面向您的 IP、系统级芯片和系统级设计验证。

HyperRam 自 2018 年投入生产,应用于诸多生产设计。

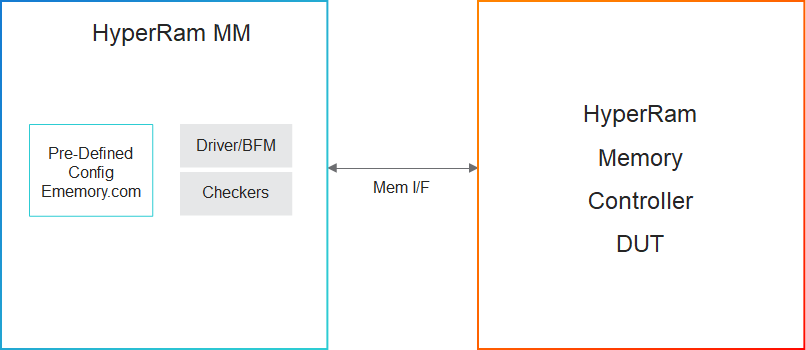

用于 HyperRam 的 Cadence® 存储器模型验证 IP (VIP) 为使用 HyperBus 和 xSPI 接口协议的 HyperRam 控制器提供验证支持。该 VIP 提供了一个成熟的、高性能的合规性验证解决方案,适用于 IP、系统级芯片 (SoC) 和系统级验证。HyperRam VIP 与行业标准的通用验证方法 (UVM) 兼容,可在所有领先的仿真器上运行,并利用行业标准的 Cadence 内存模型核心架构、接口和使用模型。

支持的规范:Cypress (Infineon) 和 Winbond 的功能。Cypress (Infineon) 的 HyperRam 器件支持两种接口:HyperBus 以及 Octal 接口,分别针对 HyperRam1.0和 HyperRam2.0。

产品优势

主要功能

下表列出了 VIP 中实现的规范的一些重要功能:

功能名称 |

描述 |

|---|---|

密度 |

|

复位 |

|

读写 |

|

突发 |

|

SHOW ALL

4 of 8

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles