Overview

Best-in-class Arm® AMBA® AHB Verification IP (VIP) for your IP, SoC, and system-level design testing.

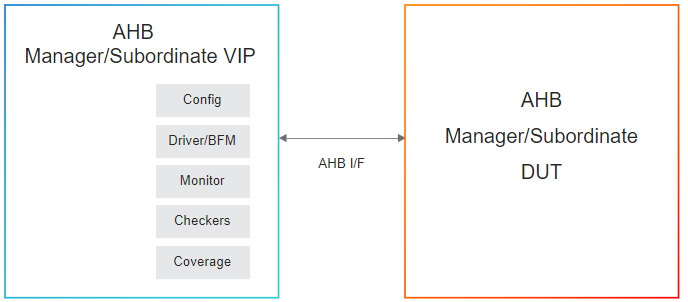

Cadence provides a mature and comprehensive Verification IP (VIP) for the AHB specification which is part of the Arm® AMBA® family of protocols. Incorporating the latest protocol updates, the Cadence® Verification IP for AHB provides a complete bus functional model (BFM), integrated automatic protocol checks, and coverage model. Cadence provides an integrated solution for interconnect verification that verifies the correctness and completeness of data as it passes through the system and performance analysis that provides automated generation of testbenches. It also provides a ready-to-use Test Suite that is composed of semi-directed tests with a limited level of randomness. The VIP for AMBA AHB is it applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification and is compatible with the industry-standard Universal Verification Methodology (UVM) and runs on all leading simulators.

Supported specification: AMBA AHB v2.0, AMBA 3 AHB-Lite Protocol v1.0, AMBA 5 AHB5 update, and Armv6 AMBA Extensions

Product Highlights

Key Features

The following table describes key features from the specifications that are implemented in the VIP:

Feature Name |

Description |

|---|---|

Multiple Agents |

|

Data and Address Widths |

|

Automatic subordinate Responses |

|

Delay Control |

|

仿真测试集合

具有覆盖模型的综合测试集合,可实现简单快速的设计和初始环境搭建(bring-up)。

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles