Overview

Best-in-class Ethernet Verification IP for your IP, SoC, and system-level design testing.

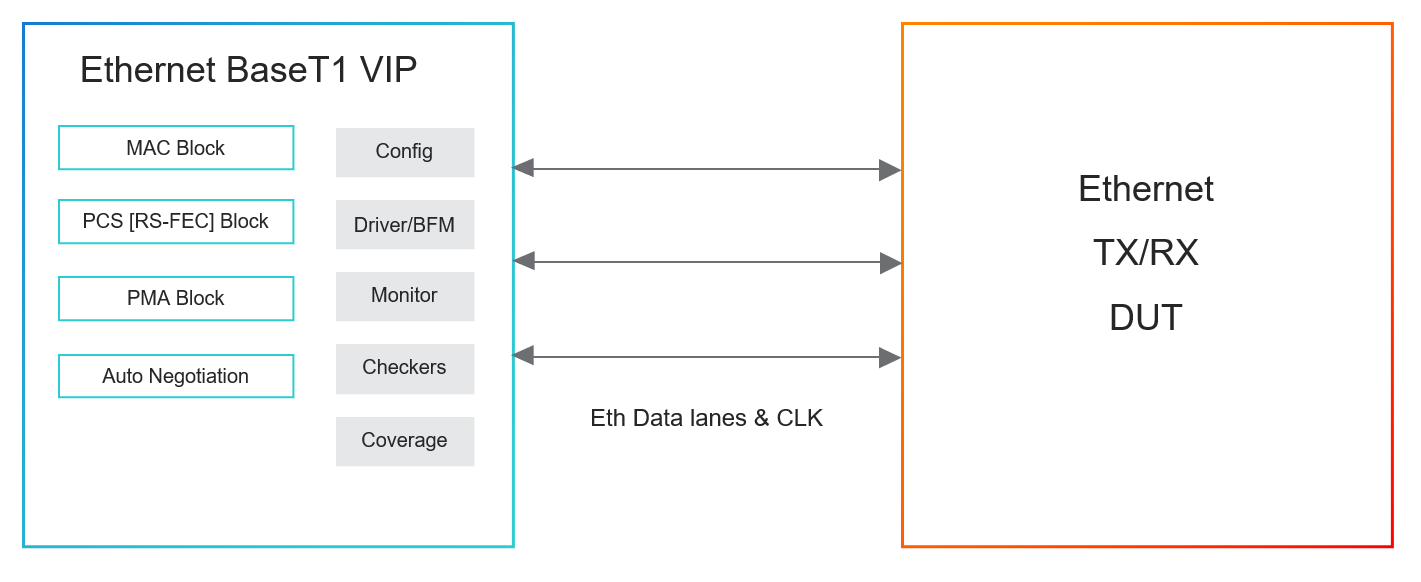

Incorporating the latest protocol updates, the mature and comprehensive Cadence Verification IP (VIP) for the Ethernet Base-T1 provides a complete bus functional model (BFM), integrated automatic protocol checks, and coverage model. Designed for easy integration in test benches at IP, system-on-chip (SoC), and system levels, the VIP for Base-T1 Ethernet helps you reduce time to test, accelerate verification closure, and ensure end-product quality. The VIP for Base-T1 Ethernet runs on all major simulators and supports SystemVerilog language along with associated methodologies, including the Universal Verification Methodology (UVM) and Open Verification Methodology (OVM).

Product Highlights

Key Features

The following table describes key features from the specifications that are implemented in the VIP:

Feature Name |

Description |

|---|---|

10 Base-T1s Interface |

Based on IEEE 802.3cg-2019 (Clause 147)

|

100 Base-T1 Interface |

Based on IEEE 802.3bw-2015

|

1000 Base-T1 Interface |

Based on IEEE 802.3bp-2016

|

| 2.5G Base-T1 Interface | Based on IEEE 802.3ch-2020

|

仿真测试集合

VIP 附带一个场景测试集合,可轻松评估和部署 VIP

如需更多信息请联系我们

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles