Overview

Maximizing Performance and Energy Efficiency for Arm-Based SoCs

Develop unique Arm-based designs quickly and more efficiently with Cadence and Arm joint solutions. We worked together to optimize performance, power, and area (PPA) while speeding design and verification processes to help you design products such as IoT and mobile devices, high-performance computing servers, and embedded applications.

Key Benefits

Accelerate Arm-Based SoC Designs with Improved PPA and Faster System Verification

We’ve worked together to optimize performance, power, and area (PPA) while speeding design and verification processes to help you design products such as IoT and mobile devices, high-performance computing servers, and embedded applications.

Achieve Best PPA

Provide highly optimized tool flows for best performance, power, and area

Faster Verification

Speed the Arm®-based design and verification process

Improve SoC Quality and Performance

Ensure IP interoperability and verification

Offerings

Over the years, our deep cooperative engineering programs join Cadence’s digital and mixed-signal design methodologies to verification flows and IP integration, and even to foundry compatibility, with Arm products including Arm Cortex®-A, Cortex-R, and Cortex-M processors; Neoverse™ processors; Mali™ GPUs, video, and display technologies; CoreLink™ System IP; Artisan® Physical IP, POP™ IP, and Fast Models.

Arm Compute Subsystem and SoC Realization Solutions

SoC compute systems have become increasingly complex over the years, involving the interaction among many sophisticated IP, including processor cores, caches, interconnect, system control, and management units, and system memory management units, not to mention interface IP such as PCI Express® (PCIe®) and DDR memory controllers. Achievement of a coherent, efficient design that is also optimized for the end application requires significant levels of engineering investment by system-on-chip (SoC) integrators. Today’s systems designers must handle these complex integrations while optimizing for system performance and power consumption, all while keeping control over the SoC’s total cost.

Cadence has worked with Arm to provide a range of complete solutions to complement Arm Neoverse Compute Subsystems (CSS). Cadence and Arm help you lower the barrier to designing custom solutions for your end applications. Cadence’s wide portfolio of Design IP, comprehensive portfolio of SoC prototyping tools, and AI-driven Verification solutions enable integrators to get to a full working SoC compute solution efficiently, allowing you to focus on adding differentiating features.

Cadence’s silicon-proven IP is designed to just work with Arm Neoverse CSS, while our AI-driven Digital Design solutions enable you to develop the design into a manufacturable physical design in record time.

If you need more support to realize your vision, Cadence, as an Arm Total Design partner offering turnkey design services, can support your CSS design flow through top-level system integration, value-added design services, and even full implementation at your foundry process with the highest level of quality.

Implementation

Arm works with EDA vendors to develop EDA reference flows. Working closely with Arm, Cadence has optimized our full-flow digital solution for Arm®-based designs. Using the resulting digital implementation reference flows, you can efficiently implement your Arm core-based systems on chip (SoCs) and reach your power, performance, and area (PPA) targets much faster versus using generic EDA reference flows.

Arm utilizes Cadence® tools to develop its IP. We have early access to Arm cores, so we can tune our tool algorithms, features, and options, and can optimize our flow before the official release of the Arm cores. This lowers your risk to develop an Arm-based SoC, reduces the timeframe to meet your PPA targets, and provides expertise to help with last-mile closure.

Verification

Developing hardware and software systems now involves integrating many IP blocks, many cores, and lots of software. To ensure that your system on chip (SoC) meets your design intent, verification technology is essential. Cadence offers verification solutions—from early software bring-up to use-case testing, debugging, and performance analysis—ideal for Arm-based SoC designs.

Collaborating with Arm, Cadence has enhanced the Arm-based system verification technologies in our System Development Suite to ensure that your Arm®-based SoCs meet design intent, minimize iterations of your interconnect, while quickly verifying and analyzing performance, and achieve faster time to market.

Verification for Arm AMBA Protocols

The most time-consuming aspect of system-on-chip (SoC) functional verification is often the creation of a testbench that accurately stimulates and responds to the interfaces on the design under test. Since a typical SoC contains dozens of standard interfaces and multiple, layered interconnect fabrics, Verification IP (VIP) provides a huge benefit by modeling all those interfaces as components that can be plugged into a testbench and simulated along with the design under test. This offloads a substantial amount of work from the verification engineer, saving time and improving product quality.

Cadence® Verification IP for Arm® AMBA® protocols is an easy-to-use comprehensive solution that improves SoC quality and performance, providing dependable results to predict verification schedules and boost productivity.

Arm SystemReady Compliance

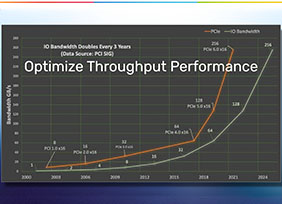

For advanced infrastructure SoC design, ensuring Arm® SystemReady compliance and achieving successful PCIe® integration are two major challenges for server architects and developers while designing Arm-based server SoCs. Checking for compliance after design completion is time-consuming and costly, as it may incorporate respins.

Cadence has been working with Arm to accelerate this compliance testing process as per the Arm SystemReady program, which ensures your design is SystemReady compliant and that a standard operating system (OS) can boot off the shelf without any custom patches.

Cadence collaborated with Arm to enable silicon partners to run the compliance suite pre-silicon through our integrated solution running on Cadence® Palladium® systems. Cadence System Verification IP accelerates the integration of PCIe controller IP and ensures compliance with SystemReady requirements.

Arm and Cadence Driving the Future of the Automotive Industry

In this video, Dipti Vachani, Senior Vice President of Automotive and IoT at Arm discusses the three megatrends disrupting the automotive industry: Electrification, ADAS and autonomy, and the digital cockpit. The increased value of electronics per car drives new challenges, including custom silicon, hardware/software co-development, cloud-native software with the SOAFEE initiative, and partnerships for functional safety like the Arm® Functional Safety Program and the Cadence® Safety Solution.

Resources