概述

优异的 Cadence MIPI® CSI-2sm 验证 IP (VIP),用于 IP、系统级芯片和系统级设计测试。

自 2008 年起投入生产,应用于数十种生产设计。

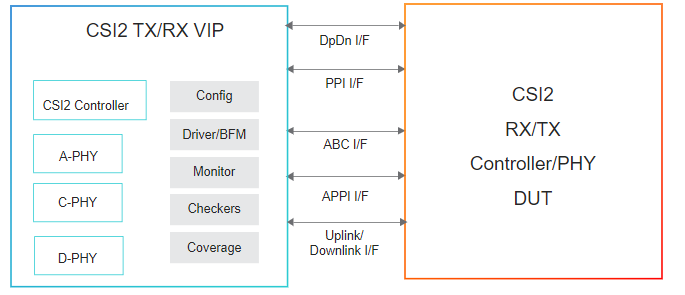

Cadence 为 CSI-2 协议提供成熟而全面的 VIP,该协议是 MIPI 系列的一部分。Cadence® CSI-2 VIP 整合了最新的协议更新,提供了完整的总线功能模型 (BFM),并集成了自动协议检查和覆盖率模型。CSI-2 VIP 可以轻松集成在 IP、系统级芯片 (SoC) 和系统层面的仿真平台中,帮助您减少测试时间,加速验证收敛,并确保最终产品的质量。VIP 可在所有主流的仿真器上运行,支持 SystemVerilog 和 e 验证语言,以及相关的方法学,包括通用验证方法学 (UVM) 和开放验证方法学 (OVM)。

支持的规范:MIPI CSI2 v1.3、v2.0、v2.1、v3.0、v4.0,MIPI D-PHY v1.2、v2.1、v2.5,MIPI C-PHY v1.0、v1.2、v2.0,MIPI CSE v1.0,MIPI PAL/CSI2 v1.0 和 MIPI A-PHY v1.0。

产品优势

主要功能

下表列出了 VIP 中实现的规范的一些重要功能:

功能名称 |

描述 |

|---|---|

PHY 接口 |

|

PPI 数据总线宽度 |

|

数据通道 |

|

数据类型 |

|

时钟 |

|

Simulation Test Suite

Extensive testsuite, coverage model, and verification plan with clear linkage to the specification for simple and fast compliance testing.

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles