Overview

Gold standard for Hyperflash memory device for your IP, SoC, and system-level design verification.

Hyperflash in production since 2018 for many production designs.

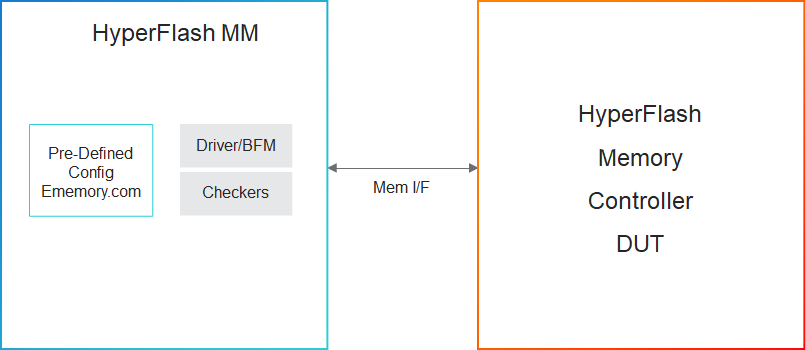

The Cadence® Memory Model Verification IP (VIP) for HyperFlash provides verification of HyperFlash Controller using the HyperBus protocol. It provides a mature, highly capable compliance verification solution applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification. The VIP for HyperFlash is compatible with the industry-standard Universal Verification Methodology (UVM), runs on all leading simulators, and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model.

Supported specification: Features of Cypress specification Document Number: 001-99198 Rev. *H Revised February 06, 2017.

Product Highlights

Key Features

The following table describes key features from the specifications that are implemented in the VIP:

Feature Name |

Description |

|---|---|

Density |

|

General Functionality |

|

Burst |

|

Reset Output Pin Functionality |

|

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles