Overview

DDR5 DIMM memory device for your IP, SoC, and system-level design verification. First to market with full DDR5 DIMM support.

First to market with full DDR5 DIMM support.

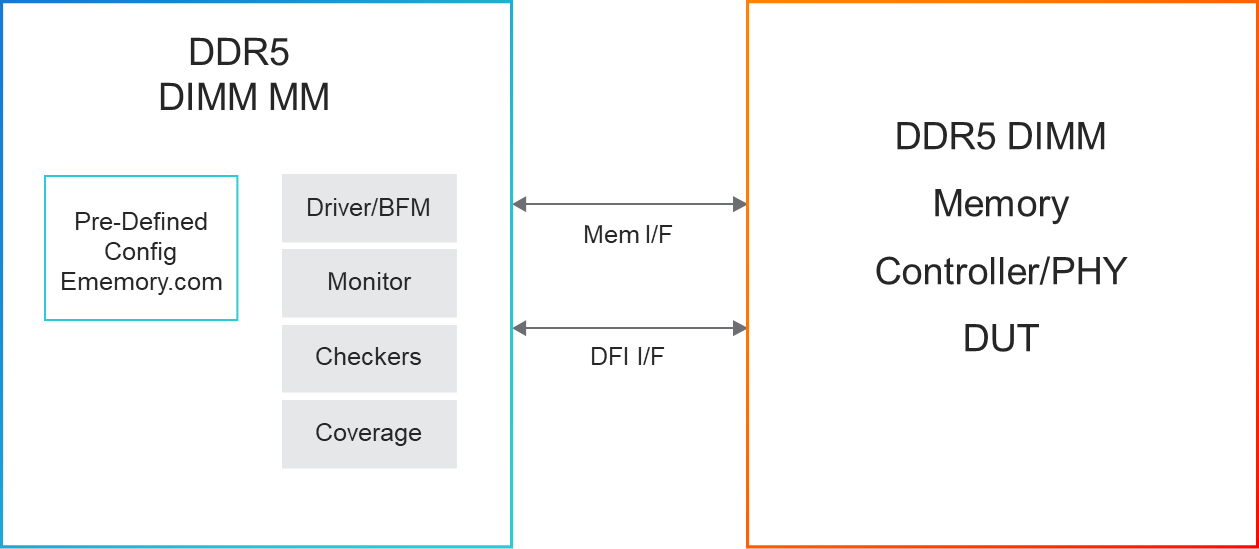

This Cadence Verification IP (VIP) provides support for the JEDEC DDR5 SDRAM Unbuffered, Registered, and Load-Reduced DIMM Design Specification, the DDR5 UDIMM/RDIMM/LRDIMM standard. It provides a mature, highly capable compliance verification solution that supports simulation and formal analysis, making it applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification. The Memory Model VIP for DDR5 DIMM is compatible with the industry-standard Universal Verification Methodology (UVM), runs on all leading simulators, and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model.

Product Highlights

Key Features

The following table describes key features from the specifications that are implemented in the VIP:

Feature Name |

Description |

|---|---|

DIMM Types |

|

Size |

|

Speed |

|

DRAMs |

|

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles