Overview

MIPI® SPMIsm Verification IP for your IP, SoC, and system-level design testing.

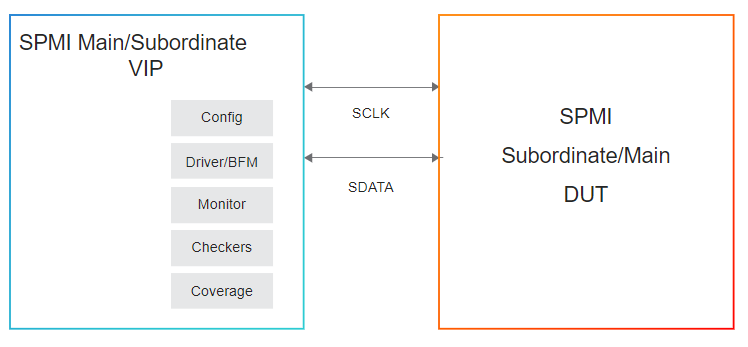

Cadence provides a mature and comprehensive Verification IP (VIP) for the MIPI® SPMIsm (System Power Management Interface) protocol. Incorporating the latest protocol updates, the Cadence® Verification IP for SPMI provides a complete bus functional model (BFM), integrated automatic protocol checks, and coverage model. Designed for easy integration in testbenches at IP, system-on-chip (SoC), and system levels, the VIP for SPMI helps you reduce time to test, accelerate verification closure, and ensure end-product quality. The VIP runs on all major simulators and supports SystemVerilog language along with associated methodologies, including the Universal Verification Methodology (UVM) and Open Verification Methodology (OVM).

Supported Specification: MIPI specifications for SPMI v1.0 and v2.0.

Product Highlights

Key Features

The following table describes key features from the specifications that are implemented in the VIP:

Feature Name |

Description |

|---|---|

Topology |

|

Clock |

|

Main Connection |

|

Main Arbitration |

|

Subordinate Types |

|

Simulation Test Suite

Comprehensive testsuite with coverage model for simple and fast design and verification bring-up.

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles