Overview

Best-in-class Arm® AMBA® Best-in-class Arm® AMBA® Distributed Translation Interface (DTI) Protocol Verification IP (VIP) for your IP, SoC, and system-level design testing.

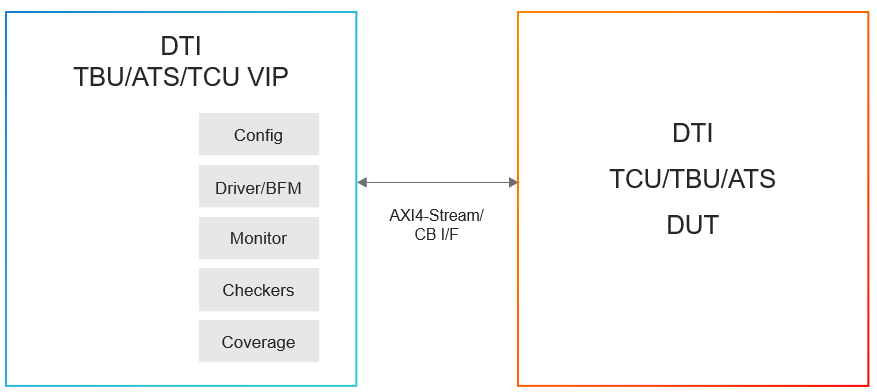

Cadence provides a mature and comprehensive Verification IP (VIP)for theDistributed Translation Interface (DTI) specification, which is part of the Arm®AMBA®family of protocols. Incorporating the latestprotocol updates, the Cadence®Verification IP for DTI provides a complete bus functional model (BFM), integratedautomatic protocol checks, and coverage model.Designed for easy integration intestbenches at IP, system-on-chip (SoC), and system levels, the VIP for DTI helps youreduce time to test, accelerate verification closure, and ensure end-product quality. Cadence provides a solution for interconnect verification that verifies the correctness and completeness of data. The VIP is compatible with the industry-standard Universal Verification Methodology (UVM) and runs on all leading simulators.

Supported specification: AMBA® DTI r0p0 Edition 3. AMBA DTI Issue F Update.

Product Highlights

Key Features

The following table describes key features from the specifications that are implemented in the VIP:

Feature Name |

Description |

|---|---|

Bypass Translation Mode Support |

|

Connect and Disconnect Message Group |

|

DTI-TBU Caching Module |

|

Invalidation and Synchronization Message Group |

|

Simulation Test Suite

VIP comes along with a testsuite of scenarios for easy VIP evaluation and deployment.

Please contact us for further information.

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles