Overview

Gold standard for JEDEC® eMMC 5.1 memory device for your IP, SoC, and system-level design verification.

In production since 2011 on dozens of designs.

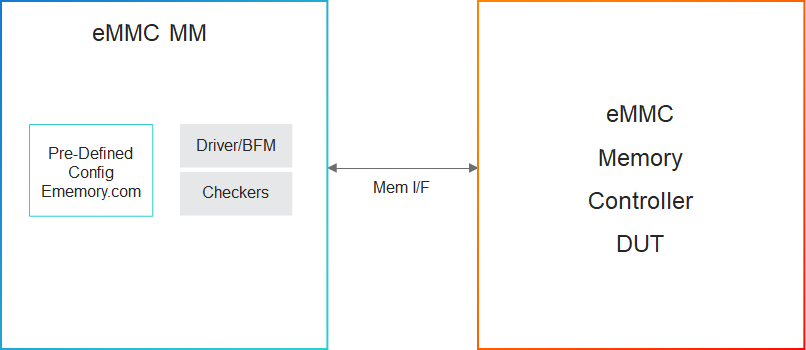

This Cadence® Verification IP (VIP) supports the JEDEC® eMMC standard. The eMMC standard is an industry-leading memory standard for embedded non-volatile storage of system code, software applications and user data. The JEDEC eMMC 5.1 standard defines functionality that focuses on improving the interaction between the host processor and the memory device at the interface, configuration and protocol levels, resulting in potential gains in overall system performance and reliability. The eMMC VIP is compatible with the industry-standard Universal Verification Methodology (UVM), runs on all leading simulators, and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model.

Supported specification: JEDEC eMMC Electrical Standard, Version 4.51 (JESD84-B451), JEDEC eMMC Electrical Standard, Version 5.0, (JESD84-B50) and JEDEC eMMC Electrical Standard, Version 5.1 (JESD84-B51)

Product Highlights

Key Features

The following table describes key features from the specifications that are implemented in the VIP:

Feature Name |

Description |

|---|---|

High speed modes |

|

General eMMC Functionality |

|

DDR Timing |

|

Address Mechanism |

|

Simulation Test Suite

MM has a rich test suite of scenarios for easy MM evaluation and deployment.

Please contact us for further information.

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles