Overview

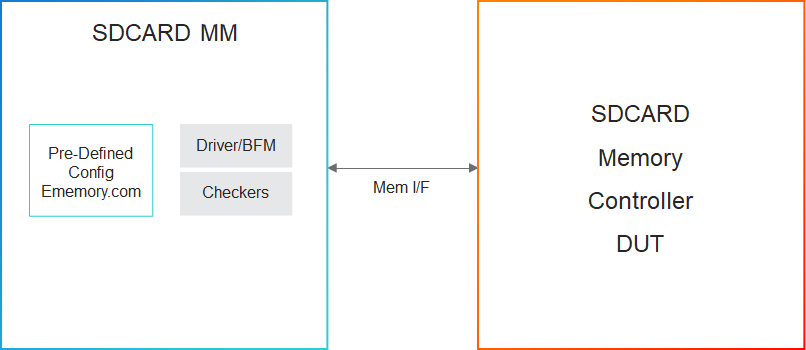

Gold standard for SD CARD memory device and SD Host Controller for your IP, SoC, and system-level design verification.

In production since 2012 for many production designs.

SD CARD Cadence Verification IP (VIP) upgrades the SD CARD and SDIO verification platform with Ultra High Speed Type II (UHS-II) support. It allows seamless verification of legacy SD CARD and SDIO protocol (version 3.00 and below) and the latest UHS-II interface. The UHS-II interface allows access to traditional SD CARD and SDIO applications through the SD-TRAN layer and to the UHS-II memory space through the CM-TRAN layer. The VIP allows full-stack UHS-II interface verification (TRAN + LINK + PHY) through the serial interface and protocol IP verification (stripped of PHY) through the PHY-LINK I/F defined in the specification.

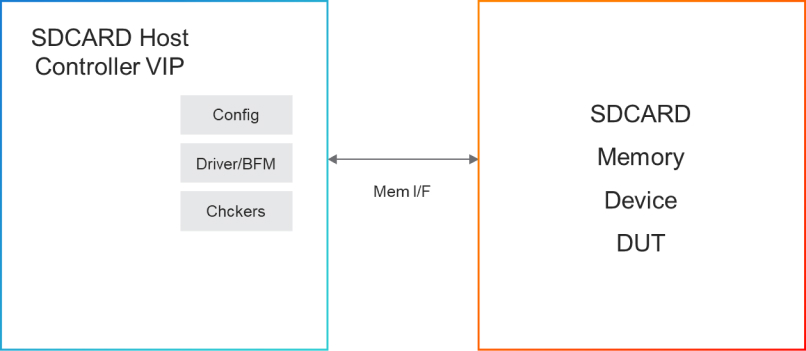

SD Host Controller Cadence Verification IP (VIP) is based on Part E1 SDIO (SD input/output) specification defined for SD and SPI bus interface specification for SDIO including register specification. It is defined for SDIO Card, Embedded SDIO device, and Combo Card.

Supported specifications:

For SD CAR – Part 1 Physical Layer Specification Version 4.00 and Part 1 UHS-II Addendum Version 1.00

For SD Host Controller – SD Specifications Part E1 SDIO Simplified Specification Version 3.00 and Part 1 Physical Layer Specification Version 3.01.

Product Highlights

Key Features

The following table describes key features from the specifications that are implemented in the VIP:

Feature Name |

Description |

|---|---|

SD Card device standard |

|

Speed Range A and B |

|

PHY-LINK I/F |

|

Half-duplex |

|

Simulation Test Suite

MM has a rich test suite of scenarios for easy MM evaluation and deployment.

Please contact us for further information.

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles