Overview

The gold standard HBM4 memory device for your IP, SoC, and system-level design verification. First to market with multiple early adopters of production designs.

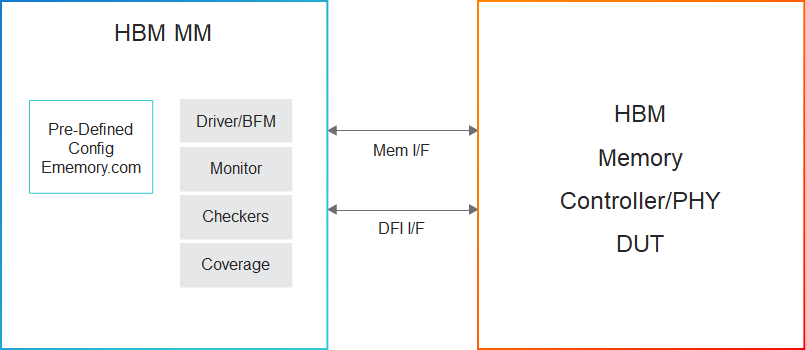

This Cadence Verification IP (VIP) supports the High-Bandwidth Memory (HBM4) interface. It provides a highly capable compliance verification solution applicable to IP, system-on-chip (SoC), and system-level verification. The Cadence Memory Model for HBM4 models a single channel of HBM4 DRAM; this model can be replicated for multiple channels and stacks. The Memory Model for HBM4 runs on all leading simulators and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model.

The HBM4 DRAM standard is an industry-leading, low-power, double-data-rate, high-data-width, volatile (DRAM) device memory standard for storage of system code, software applications, and user data. The HBM4 DRAM Memory Device Standard is designed to satisfy the performance and memory density demands of leading-edge high-performance devices.

Product Highlights

Simulation Test Suite

MM has a rich test suite of scenarios for easy MM evaluation and deployment.

Please contact us for further information.

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles