Overview

MIPI CSI-2 Transmitter

The Cadence® Transmitter (TX) Controller IP for MIPI® Camera Serial Interface 2 (CSI-2sm) is responsible for handling image sensor data in multiple RGB, YUV, and RAW formats, and user-defined data formats, while converting these into CSI-2-compliant packets for transmission over a D-PHYsm interface via the PPI interface.

The TX Controller IP for CSI-2 can handle up to four independent pixel streams and can perform Virtual Channel and Data Type interleaving before transmission four PPI data lanes.

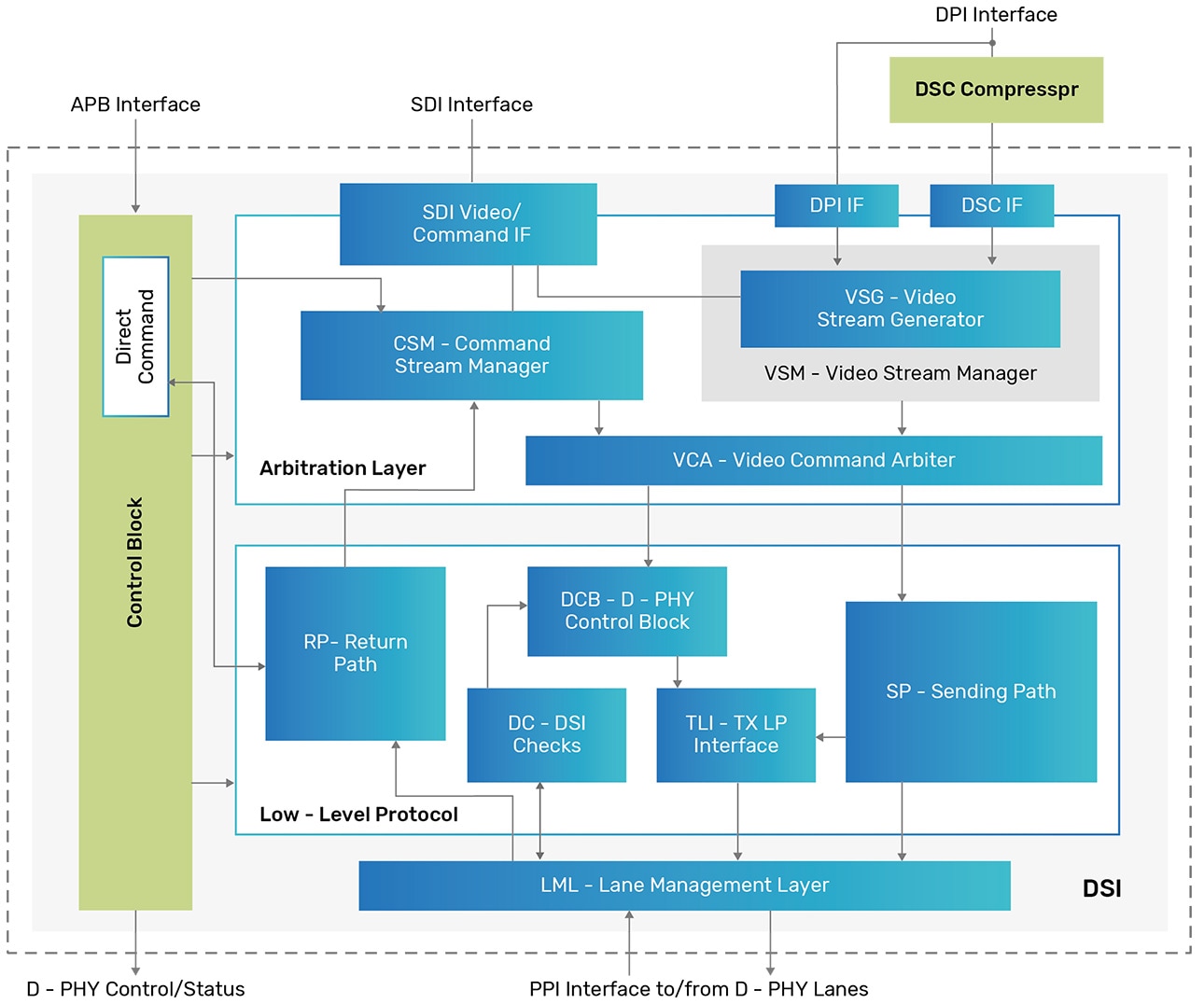

MIPI CSI-2 Transmitter Controller Block Diagram

Key Benefits

Features