Overview

MIPI CSI-2 Receiver

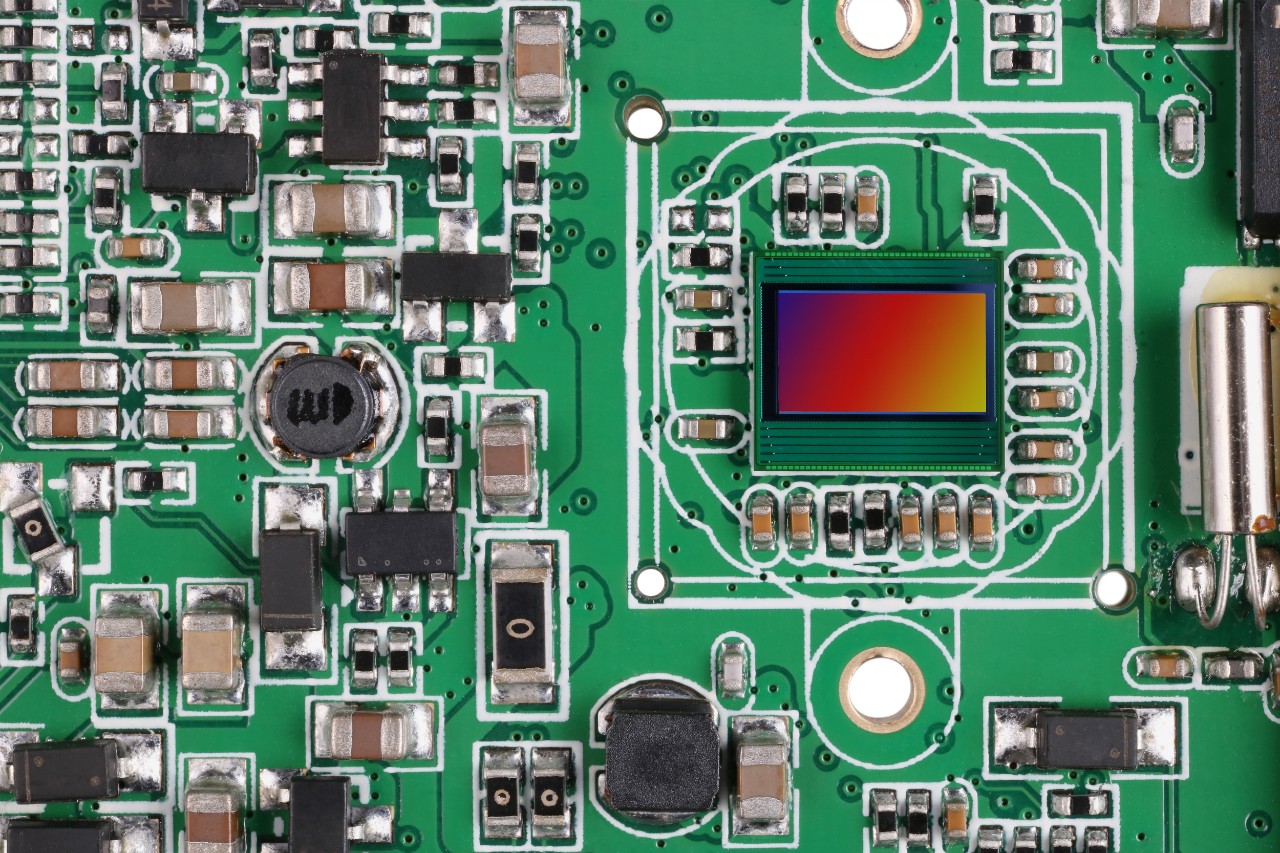

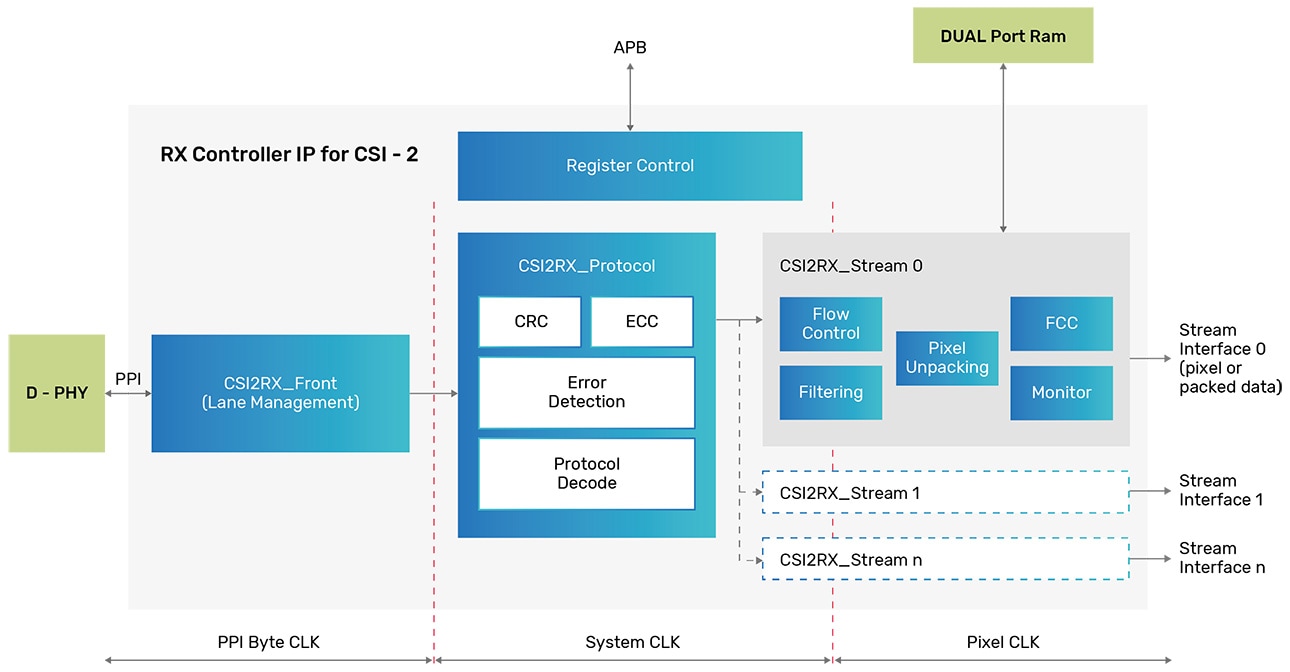

The Cadence® Receiver (RX) IP for MIPI® CSI-2sm is a fully verified, configurable, digital core that is compliant with the MIPI Alliance CSI-2 v2.1 specification. The Controller IP is responsible for handling and decoding CSI-2 protocol-based camera or other sensor data stream and managing the forwarding or unpacking of payload data to the pixel-stream interfaces. It is an ideal solution to provide a high-speed serial interface between an application or image processor and MIPI CSI-2 compliant camera sensor.

MIPI CSI-2 Receiver Block Diagram

Key Benefits

Features