Overview

Industry Leading DSP-Based 112G SerDes Solution

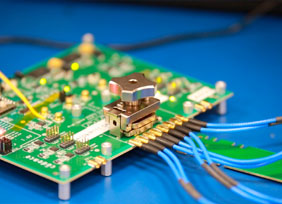

The 112G-ELR SerDes delivers exceptional extended long-reach performance with superior margin, optimized power, and area that is ideal for next-generation cloud networking, artificial intelligence and machine learning (AI/ML), and 5G wireless applications. The SerDes PHY IP supports PAM4 and NRZ signaling and data rates from 1G to 112G and incorporates industry-leading analog-to-digital converter (ADC), clock-data-recovery (CDR), and digital signal process (DSP) technology with maximum likelihood sequence detector (MLSD) that enables support up to 45dB channel.

Key Benefits

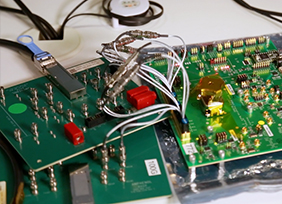

Optimal Performance with Production Quality

Production Quality

A large number of customer production tapeouts and SoC proof points.

Robust Performance

ADC/DSP-based receiver architecture with MLSD and reflection cancellation techniques provide superior data recovery for lossy and reflective channels.

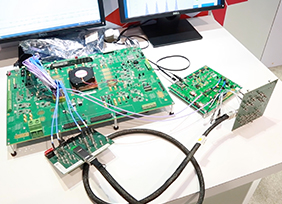

Comprehensive Testability

Rich diagnostic toolkit for easy observation and debugging.

Features

Best-in-Class PHY IP Enabling Up To 800G Subsystem Solutions

Resources

Browse Recommended Resources

Related Products