Overview

Cadence® PHY IP for PCI Express® (PCIe®) 5.0 is a high-performance SerDes configurable to operate from 1.25Gbps to 32Gbps in NRZ mode. This state-of-the-art PHY is designed specifically for infrastructure and data center applications. The SerDes’s ultra-long-reach equalization and robust clock-data recovery capabilities allow it to achieve unparalleled performance and reliability. In addition, the SerDes IP features low data path latency and low power consumption, making it ideal for deployment in time-sensitive applications in high-performance computing (HPC), artificial intelligence and machine learning (AI/ML), networking, and storage systems.

Key Benefits

Power-Efficient Design

Best-in-class power, performance, and area at PCIe 5.0 max data rates with lowest L1.2 standby power

Flexibility

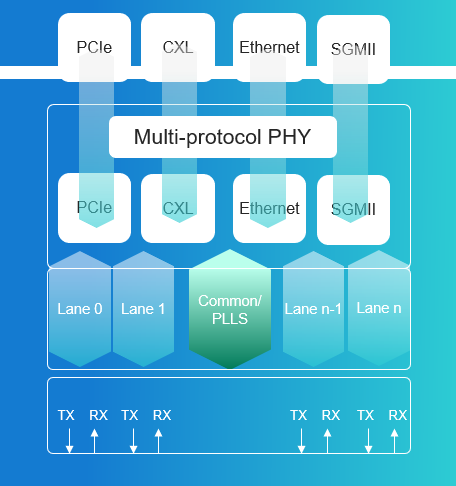

Highly configurable PHY with support for PCIe, CXL, 25G-KR, 10G-KR, SGMII, and common electrical standards such as CEI-11G/28G

Ease of use

Fully verified, pre-integrated IP delivery, with package and signal integrity support and firmware for faster bring-up

Features