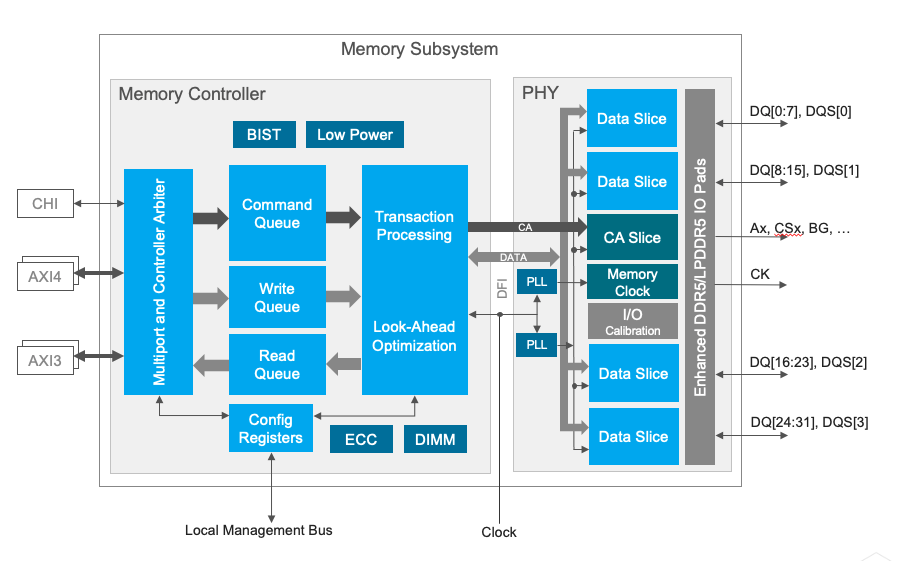

DDR/LPDDR PHY and Controller

Key Benefits

Multi-protocol Solution

DDR and LPDDR supported in a single IP

Highly Configurable

Application-specific parameters and floorplan optimization

Low Power and Area

Industry-leading PPA based on advanced architecture and implementation

Low Latency

For data-intensive applications

Reliable

Maximum system margin with advanced clocking and I/O architectures

Future proof

Cutting edge technology with the latest GDDR protocols and the highest data rates