Cadence OrbitIO - 2.5D/3DICソリューション

先端のパッケージングでは、これまでのMulti-Chip ModuleやSystem in Packageといったパッケージの設計フローではなく、ICを考慮した設計フローが必要とされてきています。ケイデンスはこれまでのパッケージフローからICセントリックフローへの置き換えに伴う様々な課題に対し、独自のソリューションを提案しています。その1つの例として、” Cadence® IC Packaging Reference Flow、TSMCの先進パッケージングソリューションで認証を取得” と銘打ってTSMC社の最新InFO、CoWoS先進パッケージングソリューションのリファレンスフロー向けの認証に関するPress Releaseを8/26に発表しましたので、こちらも参照してみてください。

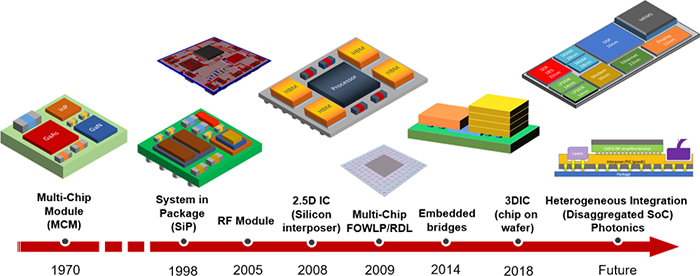

本題に戻りますが、パッケージングデザインフローは数十年にわたって進化しており、主にメカニカルベースのデザインから「PCBスタイル」のデザイン、現在は「ICフロー」対応のデザインフローに移行しています。

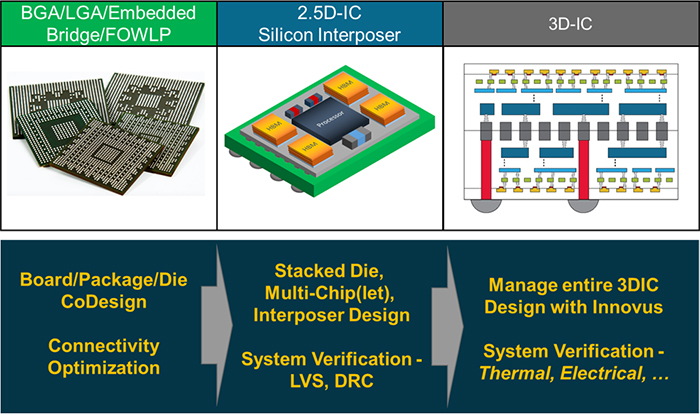

ICフロー対応のデザインの課題について考えてみましょう。

次世代ヘテロジニアスインテグレーション2.5D/3DICデザインのためのデザインツール・フローのチャレンジ

2.5D/3DICの最適なレイアウトツール・フローとは

様々なデザインタイプがある中で、自身のデザインタイプに最も適したレイアウトツール/フローは何か? これは簡単に答えられる質問ではありません。ケイデンスの3つのインプリメンテーション・ツール(Innovus®/Virtuoso®/Allegro®)はそれぞれが独自の強みを持っており、また、これらのツール・フローはさらに連携する周辺のツールにも影響を及ぼすため、これらのツール間の統合が最も重要となります。

トップレベルデザインの接続情報集約と管理

複数のチップを組み合わせる2.5D/3DIC設計においては、プリレイアウト・プランニング、システムレベルのIOプランニングが必要です。また、トップレベルのデザインのネットリスト定義(チップ間だけではなくパッケージ、PCB間も)行う必要があります。

解析と検証

高度なマルチチップICパッケージには特殊な解析と検証が必要です。3D構造を考慮したLayout vs schematic (LVS)による接続検証、チップ間のアライン・チェックなどです。

クロスドメインの電気・熱モデリング

ドメイン間のカップリングのモデリングなども考慮しなければならないかもしれません。

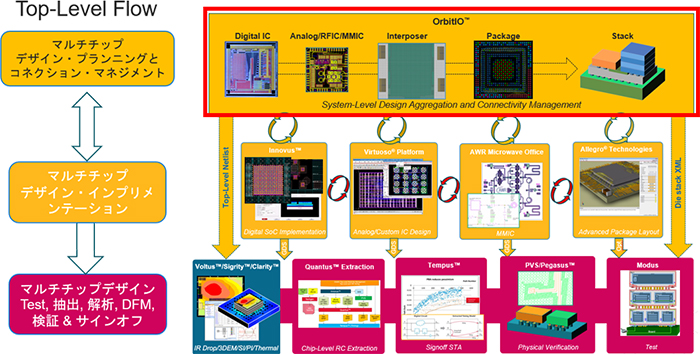

これらの課題を解決するために、Cadenceは下図のソリューションを提供しております。

Cadenceマルチチップ・先進パッケージングソリューション

このフローの特徴は、OrbitIO™ がInnovus, Virtuoso, Allegroという独自の強みをもった異なるインプリメンテーション・ツールで設計された各チップ、パッケージ、PCBのデータのトップレベルのプランニング、接続情報の一括管理しているところです。

各インプリメンテーション・ツールで設計された情報を集めてトップレベルの接続を作成し、2.5D/3DIC全体検証へ接続されます。また、DIEとDIEを接続するbumpパッドを作成することもできます。

また、OrbitIOはトップレベルデザインのプランニングツールとして使用することもでき、OrbitIOで行われた初期の検討をそれぞれのインプリメンテーションレベルのツールに組み込むこともできます。

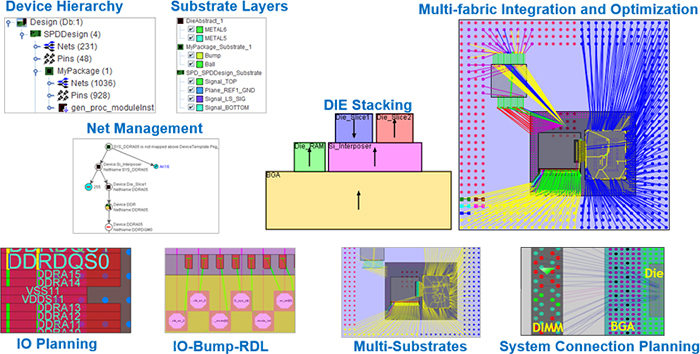

OrbitIO – System Co-design (Plan, Optimize, Manage)

OrbitIOの主な利点

- シングル・キャンバス

IC、インターポーザー、パッケージ、PCBレベルのデザインを正確に表現 - デバイスの管理

各デバイス(IC、インターポーザー、パッケージ、PCB)独自のスタックアップ コネクションはVerilogと同様に管理されます - カスタマイズ

ユーザーはスクリプトを作成し、コマンドを追加することができます - フロアプランニング

スクラッチから、2.5D/3D構造の構築、詳細なデザイン・プランニング、最適化が可能 - インテグレーション

業界標準のフォーマットを採用

インプリメンテーション・ツールと連携

2.5D/3DICのデザインフロー、フロアプランニングでお困りの際は、CadenceのOrbitIOによるトップレベルデザインを是非ご検討ください。

今回、ご紹介の内容に関しましてお問い合わせがございましたら、貴社担当営業、あるいはメール: cdsj_info@cadence.comへご連絡ください。

フィールドエンジニアリング&サービス本部

上野 博嗣

Latest Issue

- 検証作業における人工知能との新しい協力関係

- 編集後記

- 安全性とセキュリティを考慮したプレシリコンでのコンカレント・ソフトウェア開発と検証

- Virtuosoプラットフォーム、最新バージョン20.1をリリース

- AWR Design Environmentを活用した増幅器設計

- 集積型RFパッシブ・デバイスのモデリングについての考察 EMX Planar 3D Simulatorの紹介(前編)

- 集積型RFパッシブ・デバイスのモデリングについての考察 EMX Planar 3D Simulatorの紹介(後編)

- Sigrity2019 Hotfix002アップデートのご紹介

- デジタル設計・サインオフ関連webinarのビデオをCadence Online Support (COS) 上でオンデマンド配信しています!

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues