集積型RFパッシブ・デバイスのモデリングについての考察

EMX Planar 3D Simulatorの紹介(後編)

by Sharad Kapur and David E. Long

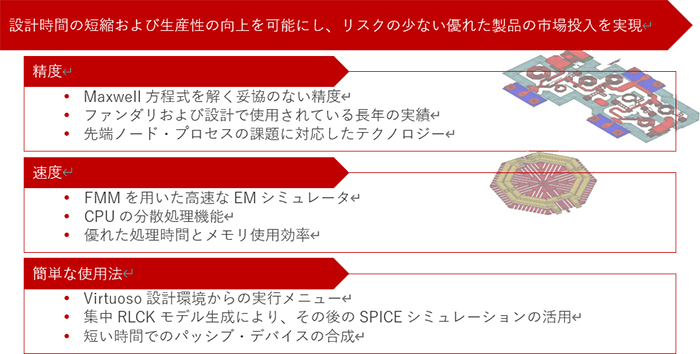

ケイデンスは、今年(2020)、5G RF通信市場に向けたイノベーションの加速に向けてIntegrand Software社を買収したことを発表しました。Integrandの製品EMX®は、市場をリードするMethod of Moments (MoM)ソルバー技術により、解析や抽出をサポートし、大規模ICや先端パッケージの高精度かつ効率の高いシミュレーション、受動部品の特性抽出、3次元ICシステムにおける配線RC寄生の解析の実現を可能にします。

この資料は、Integrand Software社時代にCICC(Custom Integrated Circuits Conference)で紹介したペーパー[22]をもとに、EMXおよび最新の電磁界シミュレータによる集積回路用のRFのパッシブ・デバイスのモデリングについて考察とEMXの魅力的な機能の紹介です。

前編では、EMXの概要、デザイン・トレンドや電磁界シミュレータの技術について紹介しました。後編では、EMXの使用した集積型RFパッシブ・デバイスのモデリングについて実測との比較など、実績について紹介します。

EXAMPLES

最新のEMシミュレータで処理が可能な問題のサイズを示す3つの例から始めます。複数のコンポーネントを含む大規模ブロックをシミュレーションする機能により、コンポーネント間の相互作用も考慮に含めたより複雑な構造をモデル化することが可能です。これらのすべての例は、8個の2.5GHz CPUと24GBのメモリを搭載したマシン上でEMXにより実行されました。シングルCPUと比較して8 CPUの速度向上は、例題の特徴とポート数により異なりますが、最大6倍まで可能です。すべての例題での入力はマスクGDSIIレイアウト・データです。例題では、手作業による編集や簡略化は行っていません。一番大きな例題でもシミュレーションの実時間は2時間未満で、これは、EMシミュレーションを「サインオフ」の最終ステップとしてのみ使用するのではなく、設計工程の一部として実行することに十分な処理速度を示しています。メモリの最大使用量は10GB未満です。

IC Diplexer

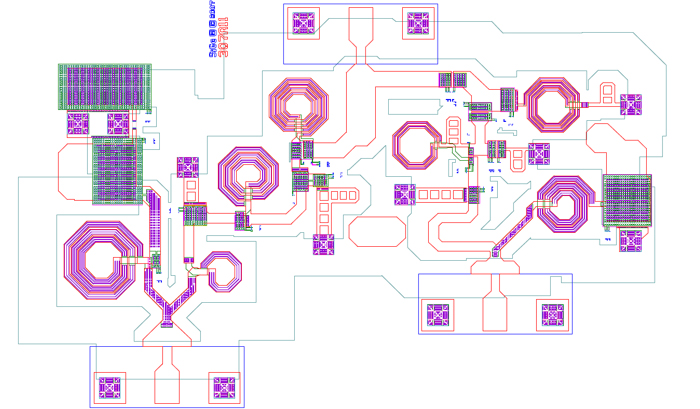

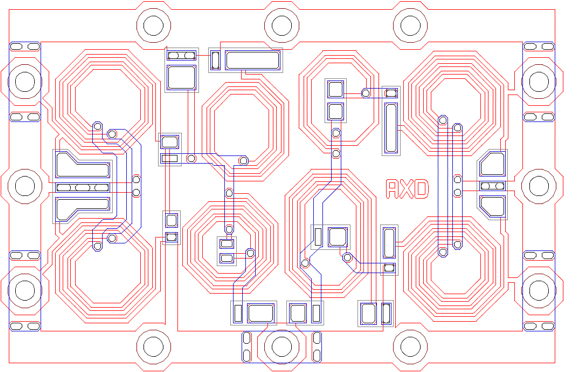

図 1は、0.18umの5層メタルのBiCMOSテクノロジーで作成された集積されたダイプレクサの例です。デザインには、レジスタ、インダクタ、MiMキャパシタ、プローブ・パッドが与えられています。主要な課題の1つは、インダクタ間およびインダクタとインターコネクト間のすべてのカップリングを考慮することです。

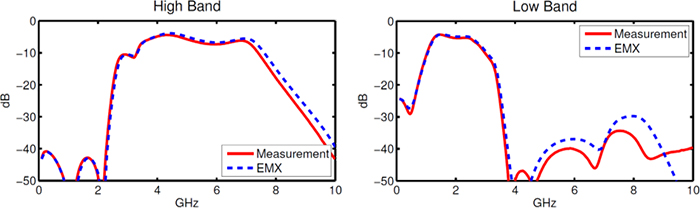

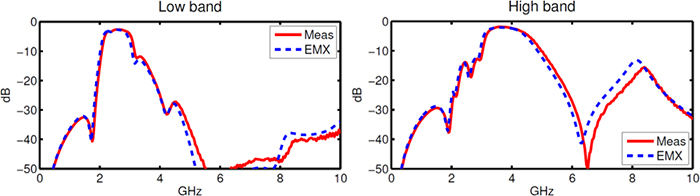

全体構造を直接シミュレーションすることで、重要な相互作用を損なうことが無くなります。ハイ・バンドおよびロー・バンドのシミュレーションと測定の応答の比較結果は十分に一致していることが分かります(図 2)。

図 1: ICダイプレクサのレイアウト

図 2: ICダイプレクサの測定とシミュレーションの比較

VCO

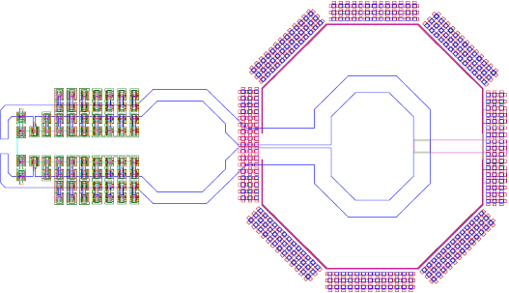

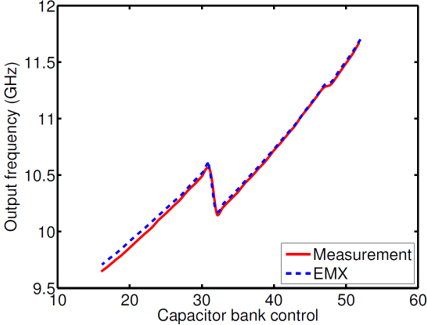

図 3は、6層メタル90nm CMOSテクノロジーで製造された集積型のVCOです。これは、チューニング用に切り替え可能な66個のMiMキャパシタのバンクと1つのインダクタで構成されています。ここでのインダクタは十分に小さいので、インダクタとインターコネクト間の寄生のカップリングとキャパシタの接続方法の詳細を考慮する必要があります。実際、ブロックごとのモデルではVCOの動作を見積もることができませんでした。全体構造をシミュレーションすることで、より正確な結果を得ることができました。チューニング特性のシミュレーションと測定の結果を図 4に示します。

図 3: 集積型VCOレイアウト

図 4: VCOチューニング特性の測定とシミュレーションの比較

IPD Diplexer

図 5は、別のダイプレクサのデザインです。このデザインはIPD(集積型パッシブ・デバイス、Integrated Passive Device)テクノロジーで作られています。このデザインは、レジスタ、インダクタ、薄膜キャパシタ、および、測定用のパッドを持っています。

図 5: IPD ダイプレクサのレイアウト

EMシミュレーションは、この設計不可欠な部分です。ダイプレクサの仕様から開始し、適切なトポロジーとコンポーネントの概算値を選択します。事前のレイアウトは、チューニング・キャパシタを接続するコイルとポートが含まれていますが、キャパシタの値はまだ確定していません。EMシミュレータから、回路シミュレータとオプティマイザで適切なキャパシタの値を探索するために使用されるモデルが生成されます。最終的なEMシミュレーションでは、(その後の測定で示すように)デバイスが仕様を満たすことを検証します。図 6にIPDダイプレクサのシミュレーションと測定結果の比較を示します。

図 6: IPDダイプレクサの測定とシミュレーションの比較

Pattern-Dependent Effects

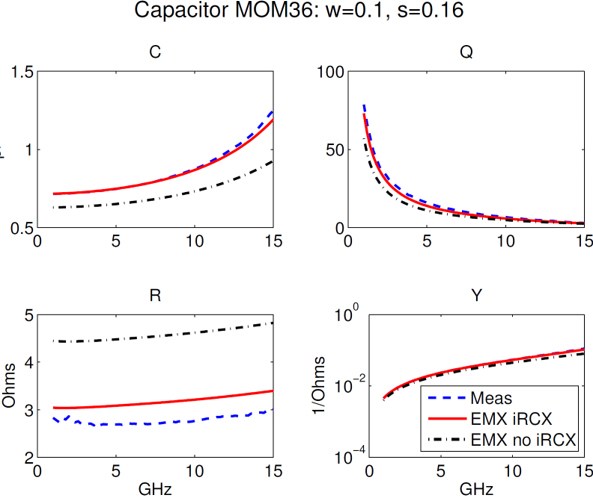

ここでは、MoMキャパシタおよびスタックド・インダクタのシミュレーションと測定結果を比較することで、パターン依存の影響の重要性について示します。テクノロジーは、TSMC 65nm 9層メタル・プロセスです。配線幅とスペーシングの依存関係はiRCXファイルで与えられいます。

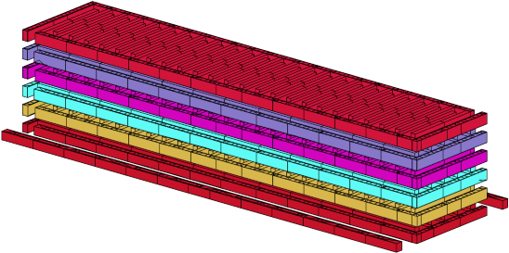

MoMキャパシタは、使用するメタルの数、メタル・フィンガーの幅、フィンガー間のスペーシングに応じて変化します。この65nmテクノロジーでは、配線幅とスペーシングの最小値はどちらも0.1umです。MoMキャパシタの1つのメッシュを図 7に示します。

図 7: MoMキャパシタのメッシュ

シミュレーションは2つ実行します。1つは最小の配線幅とスペーシングに配線プロパティを固定した(iRCXを使用しない)シミュレーションです。もう1つは、iRCXのすべての情報を使用したEMXの実行で実際のレイアウトの表現を利用したシミュレーションです。表 1にMoMキャパシタの測定とシミュレーション(低い周波数)の容量値の結果を示します。最小配線幅(0.1um)およびスペーシング(0.1um)の場合の容量値は、iRCXを使用しない場合も使用する場合の両方のシミュレーション結果が測定値と良い一致を示しています。しかし、MOM36の場合、配線幅が0.1umでスペーシングが0.16umの結果では、iRCXを使用した場合は0.2%の誤差ですが、iRCXを使用しない場合には13%の誤差となりました。この結果は、エラー! 参照元が見つかりません。のiRCXの表と関係し、バイアスが配線幅やスペーシングが増加している配線に対して非常に重要であることを表しています。

cell (w, s um) |

meas pF |

iRCX | no iRCX | ||

|---|---|---|---|---|---|

| pF | %err | pF | %err | ||

| MOM06 (0.1, 0.1) | 0.611 | 0.617 | 0.9 | 0.614 | 0.5 |

| MOM67 (0.16, 0.16) | 0.293 | 0.295 | 0.7 | 0.300 | 2.4 |

| MOM27 (0.1, 0.16) | 0.061 | 0.061 | 0.3 | 0.053 | -13.1 |

| MOM36 (0.1, 0.16) | 0.682 | 0.680 | -0.2 | 0.591 | -13.3 |

MoMキャパシタの測定とシミュレーションの結果の比較

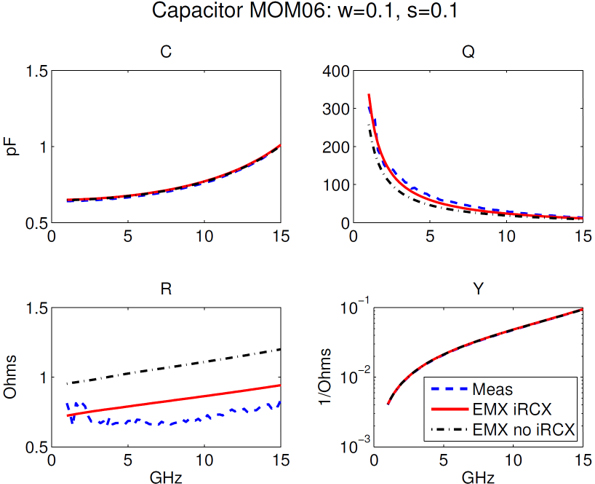

図 8と図 9にキャパシタの高周波の特性を示します。最小の配線幅とスペーシングのMOM06の結果(図 8)は、iRCXとnon-iRCXの両方のシミュレーション結果は測定結果とよく一致しています。

しかし、MOM36の結果(図 9)は、iRCXシミュレーション結果ではよく一致していますが、non-iRCXのシミュレーション結果ではCとQに大きな差異がみられます。

図 8: 最小の配線幅とスペーシングの場合のキャパシタの測定値と

MoMキャパシタのシミュレーションの比較

EMシミュレーションは、この設計不可欠な部分です。ダイプレクサの仕様から開始し、適切なトポロジーとコンポーネントの概算値を選択します。事前のレイアウトは、チューニング・キャパシタを接続するコイルとポートが含まれていますが、キャパシタの値はまだ確定していません。EMシミュレータから、回路シミュレータとオプティマイザで適切なキャパシタの値を探索するために使用されるモデルが生成されます。最終的なEMシミュレーションでは、(その後の測定で示すように)デバイスが仕様を満たすことを検証します。図 6にIPDダイプレクサのシミュレーションと測定結果の比較を示します。

図 9: 最小ではない配線幅とスペーシングの場合のキャパシタの測定値と

MoMキャパシタのシミュレーションの比較

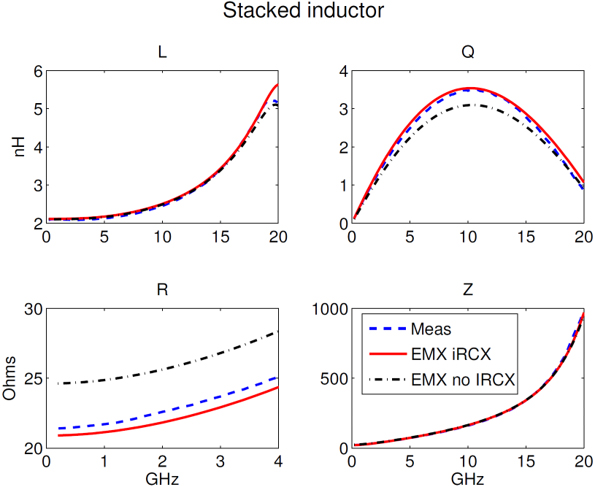

次はスタックド・インダクタのシミュレーション結果についてです。インダクタは5層メタルから9層メタルへと巻かれ、2つの薄い金属と2つの厚い金属が含まれています。インダクタのQ値は薄いメタルの抵抗値に大きく依存し、この抵抗はメタルの幅と隣接配線までのスペーシングの関数として変化します。これは、測定で観測される配線幅とスペーシングの影響です(図 10)。ここでも、配線幅とスペーシングの依存性を考慮したシミュレーションの方がより精度が高いことがわかります。

図 10: スタックド・インダクタのシミュレーションと測定の比較

Balun Modeling and Synthesis

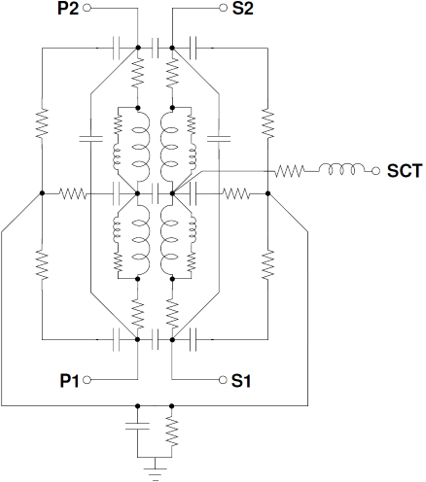

次に、コンポーネントの合成に適したスケーラブル・モデルの生成について説明します。1つの例として、オンチップ・バランを考察します。

入力として巻数比、巻き数、トレース幅、コイル径を持ったトラン・レイアウトのジェネレータから開始します。最初のステップでは、EMシミュレータを使用して、約1000の可能なトランス・レイアウトの範囲の特性を測定します。シミュレータの効率と自動化されたレイアウト処理の効果で、可能なデザイン空間(配線幅は4umから10um、巻数は2から5、巻数比は1:1から1:4、コイル径は50umから400um)のすべての網羅が1日で済みました。この回路図は、センター・タップのコイルのペア構造を示しています。

次のステップは、最適化を使って、これらの同じ物理デザイン・パラメータでパラメータ化された精度のあるスケーラブル・モデルを作成することです。スケーラブル・モデルのトポロジーは、物理的な構造の洞察から得られたもので、このトポロジーを図 11に示します。それぞれのコイルは、表皮効果をモデル化するための追加のレジスタとインダクタを持ちます。レジスタとキャパシタの組み合わせを使用して、基板をモデル化します。

図 11: スケーラブルなモデル・スケマティック

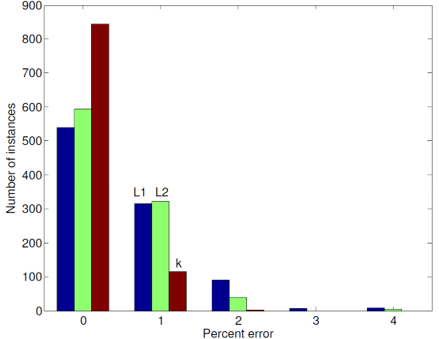

モデルの各素子は幾何学パラメータの非線形関数の値を持ちます。これらの機能の具体的な式は、物理的な洞察に基づいて選ばれます。たとえば、各コイルの主要な直列抵抗は直径に比例して幅に反比例します。関数内のフィッティング係数は、非線形の最上二乗最適化により計算されます。個々のEMシミュレーションと比較することでモデルの再生が実行され、モデルは、インダクタンス、k、Qなどの導出された値と数パーセント以内で一致することが検証されます。例えば、図 12のヒストグラムは、デザイン空間全体の一次インダクタンスL1と2次インダクタンスL2、およびkの値の誤差のパーセントを示しています。オプティマイザは数時間でスケーラブル・モデルを構築します。

図 12: モデルとシミュレーションの比較

トランスのスケーラブル・モデルが得られれば、特定のバラン(チューニング・キャパシタを含む)の性能のシミュレーションはわずか数秒で実行できます。つまり、設計空間全体の精査を1分以内に実行可能であることを意味します。制約は、面積、挿入損失、反射損失(マッチング)、位相の不均衡、振幅の不均衡の任意の組み合わせで行うことが考えられます。対象となる帯域全体を確認することができ、探索中に必要な入力インピーダンスと出力インピーダンスを指定することが可能です。EMシミュレーションとスケーラブル・モデルの作成には時間がかかりますが、与えられた任意のバランの実際の合成は非常に高速です。EMシミュレーションから得られ合成機能にリンクされたこのようなスケーラブル・モデルは、インダクタやキャパシタ、トランスやバランなどのコンポーネントのデザイン・キットの一部としていくつかのファンダリから提供されています。

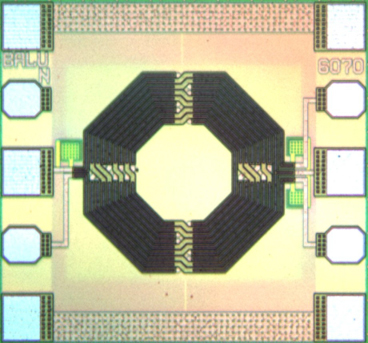

この手法は、一般的なアプリケーション(802.11A、802.11B、DCS、GSM)用の4つのバランの設計に使用されます。デモンストレーションとして、標準的なシングルエンドのインピーダンス50オームと差動出力インピーダンスの200オームを選択しています。このバランはUMCの90nmの9層ICプロセスで製造されています。コイルには3umの銅を使用し、より薄いメタルを積層してアンダーパスを形成しています。2fF/um2のチューニングMiMキャパシタを使用しています。すべてのレイアウトにおいて、コイルの面積がキャパシタの面積を占めています。製造されたバランの1つのチップ写真を図 13に示します。

図 13: 製造されたバランのチップ写真

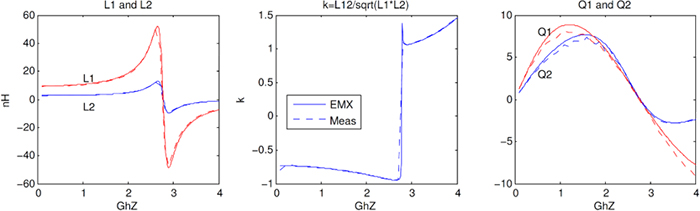

検証用に2つのセットのレイアウトを作成しました。最初のセットには、4つのポートのパッド・フレームでフローティングとなっているセンター・タップを持った4つのトランスがあります。2番目のセットはバランです。つまり、チューニング・キャパシタ(および接地されたセンター・タップ)と連動する同じトランスです。図 14に、DCSのトランスの測定とEMシミュレーションの比較を示します。結果はよく一致し、インダクタンスとkの値は、周波数帯域全体にわたり測定の数パーセント以内となっていることが確認できます。

図 14: DCSトランスのインダクタの値、kおよびQのシミュレーションと測定の比較

結果は、他の3つのトランスも同様に良好です。結果を表 2にまとめます。これは、1GHzにおけるインダクタンスとカップリングの値を示しています。

| Balun | L1(nH) | L2(nH) | k | |||

|---|---|---|---|---|---|---|

| Sim | Meas | Sim | Meas | Sim | Meas | |

| 802.11A | 1.26 | 1.25 | 3.84 | 3.83 | 0.63 | 0.64 |

| 802.11B | 2.46 | 2.42 | 8.33 | 8.17 | 0.72 | 0.72 |

| DCS | 2.86 | 2.78 | 9.79 | 9.51 | 0.74 | 0.74 |

| GSM | 6.34 | 6.11 | 22.8 | 21.9 | 0.81 | 0.80 |

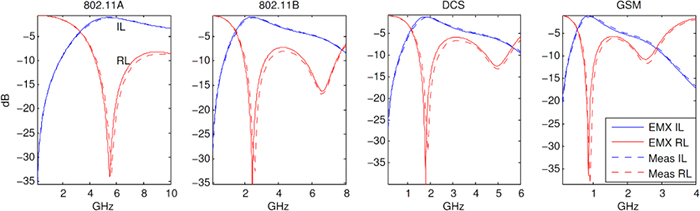

図 15に、4つのバランのEMシミュレーションと測定値との比較した結果を示します。EMシミュレーションはMiMキャパシタを含むバラン上で実行されています。すべてのバランで、測定結果とEMシミュレーションの結果の良好な一致が確認できます。挿入損失および反射損失の広帯域な特性が測定データとほぼ一致していることが確認できます。

図 15: バランの挿入損失(IL)および反射損失(RL)のシミュレーションと測定の比較

CONCLUSION

現在のEMシミュレータは、集積型RFコンポーネントをモデリングするために日常的に使うに十分なのどの処理速度と精度を持っています。この資料では、以下のような、さまざまなアプリケーションでのそのようなシミュレータの使用について考察しました。

- 複数のコンポーネントからなるデザインのカップリングの影響を考慮した解析

- 配線幅とスペーシングに関係した製造の影響を考慮した解析

- 最適化ツールを一緒に利用した、スケーラブル・コンポーネント・モデルの構築

- このようなモデルによりユーザーの仕様から最適なコンポーネント・デザインの迅速な合成が可能

この紹介では、デザイン・トレンドからの電磁界シミュレータの要望とEMX Planar 3D Simulatorの実績に追いて紹介しました。EMXはIntegrand Software社時代から17年以上も業界をリードする電磁界シミュレータです。

ACKNOWLEDGEMENTS

EXAMPLESセクションで示したデザインや測定結果について、以下の会社のご協力に感謝します。

- SiGe Semiconductor (www.sige.com)

ICダイプレクサのデザインおよび測定結果 - Wipro Newlogic

集積化されたVCOデザインおよび測定結果 - STATSChipPAC (www.statschippac.com)

IPDダイプレクサのデザインおよび測定結果 - Taiwan Semiconductor Manufacturing Company Limited (www.tsmc.com)

パターンに依存する影響を紹介するためのMoMおよびスタックド・インダクタの例題のデザイン、製造結果、測定値、およびiRCXのデータ - United Microelectronics Corporation (www.umc.com)

バランの製造結果と測定結果

REFERENCES

- EMX User’s Manual, Integrand Software, Inc., 2010.

- R. Garg, Analytical and Computational Methods in Electromagnetics. Artech House, 2008.

- J. J. H. Wang, Generalized Moment Methods in Electromagnetics. Wiley, 1991.

- L. Greengard and V. Rokhlin, “A new version of the fast multipole method for the Laplace equation in three dimensions,” Acta Numerica, vol. 6, pp. 229–269, 1997.

- Spectre Circuit Simulator User Guide, Cadence Design Systems, Inc., 2009.

- Sigrity, “Broadband SPICE,” http://www.sigrity.com.

- S. Kapur, D. E. Long, R. C. Frye, Y.-C. Chen, M.-H. Cho, H.-W. Chang, J.-H. Ou, and B. Hung, “Synthesis of optimal on-chip baluns,” in Proc. Custom Integrated Circuits Conf., 2007, pp. 507–510.

- W. C. Chew, Waves and Fields in Inhomogeneous Media. IEEE Press, 1995.

- R. Barrett et al., Templates for the Solution of Linear Systems. SIAM, 1994

- S. Kapur and D. E. Long, “Large-scale capacitance calculation,” in Proc. 37th Design Automation Conf., Jun. 2000, pp. 744–749.

- S. Kapur, D. E. Long, and J. Zhao, “Efficient full-wave simulation in layered, lossy media,” in Proc. Custom Integrated Circuits Conf., May 1998, pp. 211–214.

- K. Nabors and J. K. White, “FastCap: A multipole accelerated 3-D capacitance extraction program,” IEEE Trans. on CAD, vol. 10, no. 11, pp. 1447–1459, Nov. 1991.

- J. R. Phillips and J. K. White, “A precorrected-FFT method for electrostatic analysis of complicated 3-D structures,” IEEE Trans. on CAD, vol. 16, no. 10, pp. 1059–1072, Oct. 1997.

- Z. Zhu, B. Song, and J. K. White, “Algorithms in FastImp: A fast and wideband impedance extraction program for complicated 3-D geometries,” in Proc. 40th Design Automation Conf., 2003, pp. 712–717.

- Momentum – ADS 2009, Agilent Technologies, 2009,

http://edocs.soco.agilent.com/display/ads2009/Momentum. - “Q3D extractor,” Ansys, Inc., 2009, http://www.ansoft.com/products/si/q3d extractor.

- W. Chai, D. Jiao, and C.-K. Koh, “A direct integral-equation solver of linear complexity for large-scale 3d capacitance and impedance extraction,” in Proc. 46th Design Automation Conf., 2009, pp. 752–757.

- S. Kapur and D. E. Long, “Large-scale full-wave simulation,” in Proc. 41st Design Automation Conf., 2004, pp. 806–809.

- iRCX Unified Technology File Format Usage, TSMC, 2008, version 1.4.

- T-N65-CL-SP-009-I1 65nm iRCX file at http://online.tsmc.com, TSMC, 2008.

- T. Imai, “A topology-oriented algorithm for the Voronoi diagram of polygons,” in Proc. 8th Canadian Conference on Computational Geometry, 1996, pp. 107–112.

- S. Kapur and D. E. Long, “Modeling of Integrated RF Passive Devices,” IEEE Custom Integrated Circuits Conference 2010.

(訳)

フィールドエンジニアリング&サービス本部 カスタムIC&シミュレーション&SPB

菅谷 英彦

Latest Issue

- 検証作業における人工知能との新しい協力関係

- 編集後記

- 安全性とセキュリティを考慮したプレシリコンでのコンカレント・ソフトウェア開発と検証

- Virtuosoプラットフォーム、最新バージョン20.1をリリース

- AWR Design Environmentを活用した増幅器設計

- 集積型RFパッシブ・デバイスのモデリングについての考察 EMX Planar 3D Simulatorの紹介(前編)

- Cadence OrbitIO - 2.5D/3DICソリューション

- Sigrity2019 Hotfix002アップデートのご紹介

- デジタル設計・サインオフ関連webinarのビデオをCadence Online Support (COS) 上でオンデマンド配信しています!

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues