集積型RFパッシブ・デバイスのモデリングについての考察

EMX Planar 3D Simulatorの紹介(前編)

by Sharad Kapur and David E. Long

ケイデンスは、今年(2020)、5G RF通信市場に向けたイノベーションの加速に向けてIntegrand Software社を買収したことを発表しました。Integrandの製品EMX®は、市場をリードするMethod of Moments (MoM)ソルバー技術により、解析や抽出をサポートし、大規模ICや先端パッケージの高精度かつ効率の高いシミュレーション、受動部品の特性抽出、3次元ICシステムにおける配線RC寄生の解析の実現を可能にします。

この資料は、Integrand Software社時代にCICC(Custom Integrated Circuits Conference)で紹介したペーパー[22]をもとに、EMXおよび最新の電磁界シミュレータによる集積回路用のRFのパッシブ・デバイスのモデリングについて考察とEMXの魅力的な機能の紹介です。

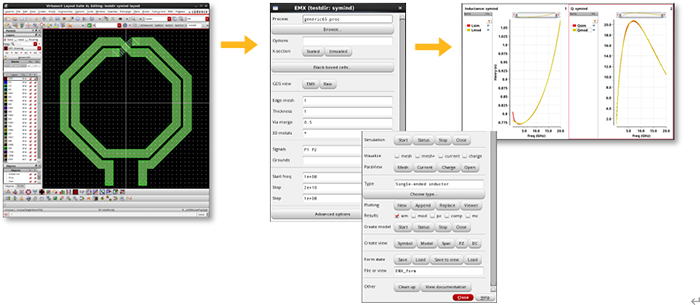

EMXは、Fast Multipole Method(FMM)に基づいたICデザインの高速なEM(電磁界)シミュレータです。Virtuoso環境とシームレスに統合され、Virtuoso Layoutからの迅速な解析や結果の解析、および、等価モデル(Sパラメータや回路図)を簡単に生成できます。EMXから出力された等価モデルを利用して、ADEからのシミュレーションの実行など、Virtuosoからの使い勝手の良い環境を提供します。EMXは、主要ファンダリのPDK作成にも採用され、また、EMX用のPDKが用意されているために、ユーザーは、すぐに使用することができます。

この種の電磁界シミュレータは、高精度を必要とするRFデザインの受動素子(例えば、インダクタ)のモデリングに使用されてきました。近年、高速化したクロックで動作するデザインのクリティカルなインターコネクトにおいて、従来よりも高精度なモデル化が必要となっています。電磁界シミュレータを利用してSパラメータのモデル化する要望も増えています。Virtuoso環境から簡単に使うことができるEMXを利用することで、既存の設計環境や設計フローを保ったまま高精度な配線のモデリングを実現することが可能です。

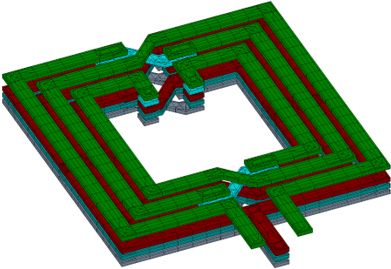

図 1: EMXのVirtuosoからの実行(Virtuosoとのシームレスな統合)

ABSTRACT

近年のEMシミュレータは、集積型RFコンポーネントの良いモデルを作成するために、十分な速度と精度を持っています。先端ノード・プロセスの重要な現象に、周囲のワイヤの影響によって、ワイヤの物理特性(幅、厚さ、抵抗値)が変化するということがあります。本稿では、プロセス情報からの配線幅と間隔に依存する特性についてのEMXシミュレータ[1]の対応について紹介します。EMXシミュレータでは、手作業による簡略化を必要とせずにマスク・レイアウトを処理するため、数千の可能性のあるデザインをシミュレーションしてスケーラブルなコンポーネント・モデルの構築が可能です。このようなスケーラブル・モデルにより、ユーザー指定の仕様を満足する適切なコンポーネントをすばやく選択することを可能にします。

INTRODUCTION

テクノロジーのトレンドにより、オンチップのパッシブ・コンポーネントがますます普及しています。厚いメタルと高抵抗基板は、高品質のオンチップのインダクタやトランスおよびバランを可能にします。

例えば、オフチップのLTCC(Low Temperature Co-fired Ceramics)バランやセラミック・バランに匹敵する挿入損失をもった集積型のバランで設計することができます。微細形状("0.1μm" 以下)と多配線層(10層以上)により、高密度の集積型(MoM、Metal-Oxide-Metal)キャパシタの設計も可能です。ICのプロセスは誤差が厳しいため、チップ間のばらつきも小さくなります。そして、もちろん、集積によりコスト削減も考えられます。普及率が高いことから、集積されたパッシブ・コンポーネントの高速かつ高精度なモデリング手法が重要となります。このモデリングでは、以下の項目が大切です。

- 候補の物理デザインを評価し場合により物理デザインを改善するためのEMシミュレーション

- 回路ネットリスト・レベルなどの上位レベルのシミュレータで使用できるモデルにEMシミュレーションの結果を変換する機能

EMシミュレータは2つの大きなカテゴリに分けることができます。1つはMaxwell方程式の微分式に基づくもので、もう1つはMaxwell方程式の積分式に基づくものです。前者の例としては、有限差分法(finite difference method)(周波数領域と時間領域の両方)と有限要素法(finite element method)シミュレータが含まれます[2]。これらは柔軟ですが、物理的導体を取り囲む大きく適切な空間を含む誘電体を離散化しなければならないという短所があります。これは、自明でない場ではMaxwell方程式を適用する必要があるからです。積分式(もしくは境界要素法)[3]は、一般に周波数領域の計算で、囲んでいる誘電体媒体がほぼ平面の場合に、適切な計算方法です。これらは、周囲の誘電体ではなく、導体のみの離散化を必要とします。ICのパッシブの場合、平面性は良い近似法です。さらに、境界要素法を効率的に実装する方法について理解は、特に高速多重極法(Fast Multipole Method、FMM)や関連した技術の開発により、深まりました[4]。概して、通常、周波数領域の積分法は、適用可能な場合に最も効率的な選択で、このことから、ICパッシブのシミュレーションに最も適した手法といえます。本稿では、主にこの手法について考察を進めます。

周波数領域のシミュレーション・データを回路シミュレータに適した形式に変換することは、一般的な場合では難しい問題です。しかし、コンポーネントの基本的な種類をモデル化するというより制約のある領域では、2つの基本的なアプローチが考えられます。1つは、オプティマイザを使用して、デバイスに適したユーザー指定の回路トポロジーのパラメータを探索することです。一般に非線形最適化は困難ですが、このアプリケーションでは適切に動作します。ポールゼロ・フィッティングに基づいた手法も実行可能です。受動性を維持するように注意する必要がありますが、商用ツールでは、回路シミュレータに内蔵されているもの[5]やスタンドアローンのアプリケーション[6]の両方で利用できます。個々のパッシブ・コンポーネントのモデリングには、最適化もしくはポールゼロ・フィッティングが適しています。また、最適化の場合は、スケーラブル・モデルの作成が可能です。スケーラブル・モデルは、物理量によってパラメータ化されます。例えば、スケーラブルなインダクタ・モデルは、巻き数、直径、ワイヤ幅、巻き間隔のパラメータによりパラメータ化することが可能です。スケーラブル・モデルは、可能なコンポーネントの設計空間全体を取り込みます。スケーラブル・モデルを使用することで、設計空間全体を探索してユーザー指定の仕様から、最適なデザインを迅速に合成することが可能です[7]。

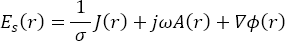

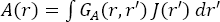

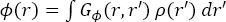

INTEGRAL FORMULATIONS FOR EM SIMULATION

積分式に基づくプレーナーEMシミュレータは、周囲の誘電体ではなく導体の離散化のみを必要とします。誘電体および基板のすべての影響は、グリーン関数の式により暗黙的に取り込まれます[8]。周波数領域では、r の点の刺激電界 Es は、オーム損失、ベクトル・ポテンシャル A、および、スカラー・ポテンシャル ϕ から生じる電界と一致する必要があります。

ベクトル・ポテンシャルとスカラー・ポテンシャルは、導体にわたり積分することで得られます( および

および  )。J は電流密度です。ρ は電荷密度です。GA はベクトル・ポテンシャルのグリーン関数です。Gϕはスカラー・ポテンシャルのグリーン関数です。コンピュータ・シミュレーションの場合、この連続方程式は、導体を個別のメッシュ要素(それぞれ未知の電荷および/または電流を持った)に分割することで離散化します。積分は有限和となり問題は線形システムとして表されます。

)。J は電流密度です。ρ は電荷密度です。GA はベクトル・ポテンシャルのグリーン関数です。Gϕはスカラー・ポテンシャルのグリーン関数です。コンピュータ・シミュレーションの場合、この連続方程式は、導体を個別のメッシュ要素(それぞれ未知の電荷および/または電流を持った)に分割することで離散化します。積分は有限和となり問題は線形システムとして表されます。

導体表面全体の積分のため、離散化後に、積分式は線形方程式の密なシステムを形成します。つまり、あるメッシュ要素の小さな電流や電荷が他のすべてのメッシュ要素の電位に影響を与えることを意味しています。

このような方程式の密なシステムを扱うことで、積分式を使用する初期のシミュレータは、(積分式では少ない数の離散化要素しか必要としなかったという事実にも関わらず)、微分式を使用するシミュレータと同程度の速度でした。線形システムを解くための反復計算法[9]と、ポテンシャルを含む積分により形成される線形システムをコンパクトに表すための技法[4]のその後の研究により、積分式のシミュレータの速度が大幅に向上しました。研究機関([10]、[11]、[12]、[13]、[14])からの第1世代の高速フィールド・ソルバーで開拓された技法は、Agilent社のMomentum [15]、Ansoft社のQ3D Extractor [16]、および、Integrand Software社のEMX [1]などの商用製品に採用されています。これらのツールにより、速度とメモリ効率がさらに向上しました。高速なダイレクト・ソルバーの使用など、さらなる改良が、アカデミックのコンテキストとして登場しています[17]。我々はEMXに精通しているため、ここではEMXが使用するいくつかの改良について論じたいと思います[18]。

ICレイアウトを正確にモデル化するには、表皮効果(skin-effect)とサイドウォール・キャパシタンスを正しくシミュレーションすることが重要です。特にMoMキャパシタの場合、薄い導体を用いた「2.5D」の近似では不十分です。図 2に示すように、導体とビアを真の3Dオブジェクトとして扱うように体積積分法を使用しています。

図 2: スタックド・インダクタの3Dメッシュ

EMXはベクトル・ポテンシャルの相互作用(一般的にシミュレーションの中で最も計算負荷の掛かる部分)に、特別な表現を用いています。この表現により、ベクトル・ポテンシャルの相互作用は、スカラーの相互作用とほぼ同等の計算負荷で処理することができます。この手法は、電流を発散のない部分と渦のない部分に分解することに依存しています。発散のない部分は、ベクトル・ポテンシャルに支配的に寄与する部分で、これらは正確に取り込まれます。渦のない部分の重要度の低い寄与は、1%よりもわずかに良い精度で概算され、これはICの問題に十分な精度です。

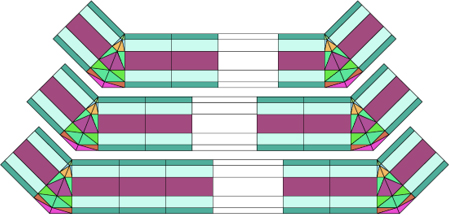

典型的なICレイアウトは非常に規則的です。サブサーキットやコンポーネントの繰り返されるインスタンスを越えて、ワイヤは一定の幅のパスとなる傾向があり、通常は隣接配線間の距離は一定で、ほとんどの配線は90度もしくは45度の角度となります。シミュレータは規則性を利用することで、時間とメモリの使用量の削減が可能です。インダクタのメッシュの繰り返されるシェイプを図 3に示します。

図 3: 同じ形状(の繰り返し)でシェーディングされた配線のメッシュ

実際には、自動化は、シミュレーション速度やメモリ使用効率と同じように重要なことです。レイアウトをシミュレータに取り込むための適切な形にするために大幅な手作業による編集が必要な場合、手作業がボトルネックとなってしまいます。多くの商用EMシミュレータは主要なICデザイン・システムへのインターフェイスがあり、ビアのマージなど、タスクを自動化する方法を備えています。EMXは、ビア・アレイやコンテキスト依存のコンタクト、メタル・フィルやメタル・スロットなど、今日のICレイアウトの一般的な機能を自動的に処理することができます。

PATTERN-DEPENDENT EFFECTS

先端ノード・プロセスの1つの特徴は、一般に、配線の物理的な幅、厚さ、抵抗値は周囲の配線から影響を受けます。時には、ばらつきが非常に問題になることがあります。製造された配線幅は、ノミナル(作成された)の配線幅から最大50%ばらつくことがあり、シート抵抗は2倍に変化する可能性があります。このようなばらつきは「pattern-dependent effects」(パターン依存の影響)と呼ばれています。これらの効果は非常に大きくなることがあるため、シミュレーションやモデリングでこの効果を考慮することは重要です。

いくつかのファンダリは、パターン依存性の詳細な情報を提供しています。通常、この情報はテーブル形式のデータで、この表は、配線幅と隣接する配線とのスペーシングによりインデックスが与えられています。1つの例は、TSMCのR (L) C抽出テクノロジー・ファイル・フォーマットiRCXです[19]、[20]。このファイル・フォーマットは、スタティックなRLC抽出および高周波EMシミュレーションの両方に使用されています。

シミュレータで使用されるプロセス記述では、材料特性のすべての定義(誘電率や導電率など)および、すべてのクロスセクションの寸法(レイヤ、導体の厚さ)が含まれている必要があります。EMXからも、導体のプロパティを定義して、幅とスペーシングの依存性を含めることができます。内部的には、入力レイアウト(描画レイアウト)は、製造された構造を正確にモデル化するために自動的に変更されます。パターン依存性の影響を処理するには、以下の項目が必要となります。

- ローカルの配線幅とスペーシングの適切な定義を考案し、これらの量を計算する効率的なアルゴリズムの開発

- それらの機能として入力ジオメトリの操作

これらのステップを、次のサブセクションで論じます。

Computing Width and Spacing

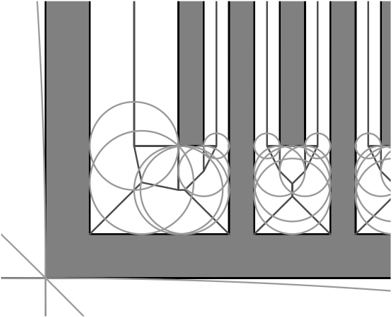

単純な繰り返しパターンのレイアウト(例えば、複数の並列配線)では、配線幅とスペーシングには直感的な意味があります。しかし、シミュレータでは、不均一なレイアウトを含むより複雑な状況を処理することが必要です。通常の領域で直感的な意味と一致し効果的な計算に利用できる定義が必要です。配線幅とスペーシングについて、オブジェクト間の局所的な距離を表すための自然な幾何学的データは、ボロノイ図(Voronoi diagram)です[21]。

レイアウトの場合、対象となるオブジェクトは、配線のエッジを表すライン・セグメントと、セグメントを接続するポイントの部分です。各セグメントとポイントには、他のオブジェクトよりもそのオブジェクトに近い領域を持ちます。この考えに従って、平面全体が重複しない領域に分割されます。この分割が、セグメントとポイントのボロノイ図です。ボロノイ図の一部が配線の中に位置して、残りの部分が外側に位置します。これらの2つの部分は、内部ボロノイ図と外部ボロノイ図と呼ばれます。

MoMキャパシタのレイアウトの一部と関連した外部ボロノイ図を図 4に示します。網掛けの部分は配線を表します。配線の間に、ボロノイ領域の境界を表す複数のセグメントがあります1。さらに、複数の最大内接円が示されています。そのような円は3つのオブジェクトに触れるだけで、これらのオブジェクトに触れている間、この円を大きくすることができません。

1 技法としては、いくつかの境界は放物線の一部ですが、計算上、セグメントによりこれらの部分を近似するほうが簡単です。

図 4: 複数の配線の外部ボロノイ図

ローカルなスペーシングは、最も近い他のオブジェクトやセグメントに接する適切な最大内接円の直径から得られます。ローカルな幅は、外部ボロノイ図の代わりに内部ボロノイ図に基づいて、ローカルなスペーシングと同じ方法で計算されます。ローカルな幅とスペーシングはボロノイ図の作成時にレイアウト全体の重要な個所で計算されます。その後、任意の所望の位置で値がすばやく補間されます。

Mimicking Fabrication Effects

一般に、製造に最も重要な影響は、物理的な配線幅が、レイアウトのローカルな幅とスペーシングに依存するバイアス量により、描画された幅からのずれになります。バイアス量は、ファンダリから提供されたテーブルから得ることができます。表 1は、メタル配線の物理的な幅と描画された幅とスペーシングの依存性について示した例です。例えば、この表から、スペーシングが0.2μmの時の0.1μmの幅の描画配線の物理的な配線幅は0.147μmとなります。これは、描画された配線幅が約50%広くなることを表してします。

| w\s | 0.1000 | 0.1300 | 0.1500 | 0.2000 | … |

|---|---|---|---|---|---|

| 0.1000 | 0.1025 | 0.1125 | 0.1220 | 0.1470 | … |

| 0.1300 | 0.1265 | 0.1285 | 0.1340 | 0.1525 | … |

| 0.1500 | 0.1459 | 0.1459 | 0.1459 | 0.1599 | … |

| 0.2000 | 0.1783 | 0.1783 | 0.1783 | 0.1783 | … |

| … | … | … | … | … | … |

ばらつきの例

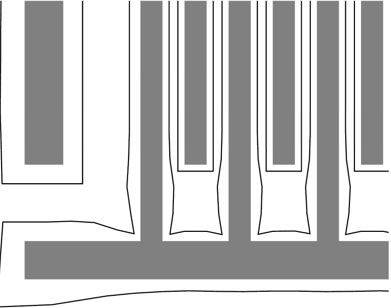

このようなテーブルによる補間は、描画される配線幅とスペーシングの関数としてのバイアスの、連続関数を生成します。そのような可変バイアス演算の前と後のレイアウトの例を図 5に示します。大切な点は、配線幅やスペーシングが均一ではないので、バイアスされた図形は直線的ではなくなります。

図 5:バイアスされる前(灰色)と後(アウトライン)の配線

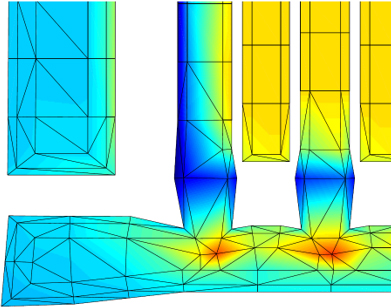

もう1つの重要な影響はシート抵抗のばらつきです。ローカルは配線幅およびスペーシングと、バイアスされた図形が計算された後に、シミュレータは通常通りにメッシュ生成を行うことができます。次に、メッシュの各ポイントで、配線幅とスペーシングの関数としてシート抵抗が計算できます。メッシュ内の各シェイプでは、シェイプの面積で平均化することによりシート抵抗が計算されます。表 2に、抵抗のばらつきの例を示します。シート抵抗は、配線幅とスペーシングの関数としてほぼ2倍に変化していることに注意してください。図 6にMoMキャパシタのシート抵抗のばらつきを示します。

| w\s | 0.1000 | 0.1300 | 0.1500 | 0.2000 | … |

|---|---|---|---|---|---|

| 0.1000 | 0.1399 | 0.1220 | 0.1084 | 0.0839 | … |

| 0.1300 | 0.1355 | 0.1316 | 0.1235 | 0.1034 | … |

| 0.1500 | 0.1285 | 0.1275 | 0.1266 | 0.1116 | … |

| 0.2000 | 0.1315 | 0.1305 | 0.1295 | 0.1286 | … |

| … | … | … | … | … | … |

実際のシート抵抗(ohm/square)のばらつきの例

図 6: メッシュのシート抵抗のばらつき

以降、後編につづきます。

REFERENCES

- EMX User’s Manual, Integrand Software, Inc., 2010.

- R. Garg, Analytical and Computational Methods in Electromagnetics. Artech House, 2008.

- J. J. H. Wang, Generalized Moment Methods in Electromagnetics. Wiley, 1991.

- L. Greengard and V. Rokhlin, “A new version of the fast multipole method for the Laplace equation in three dimensions,” Acta Numerica, vol. 6, pp. 229–269, 1997.

- Spectre Circuit Simulator User Guide, Cadence Design Systems, Inc., 2009.

- Sigrity, “Broadband SPICE,” http://www.sigrity.com.

- S. Kapur, D. E. Long, R. C. Frye, Y.-C. Chen, M.-H. Cho, H.-W. Chang, J.-H. Ou, and B. Hung, “Synthesis of optimal on-chip baluns,” in Proc. Custom Integrated Circuits Conf., 2007, pp. 507–510.

- W. C. Chew, Waves and Fields in Inhomogeneous Media. IEEE Press, 1995.

- R. Barrett et al., Templates for the Solution of Linear Systems. SIAM, 1994

- S. Kapur and D. E. Long, “Large-scale capacitance calculation,” in Proc. 37th Design Automation Conf., Jun. 2000, pp. 744–749.

- S. Kapur, D. E. Long, and J. Zhao, “Efficient full-wave simulation in layered, lossy media,” in Proc. Custom Integrated Circuits Conf., May 1998, pp. 211–214.

- K. Nabors and J. K. White, “FastCap: A multipole accelerated 3-D capacitance extraction program,” IEEE Trans. on CAD, vol. 10, no. 11, pp. 1447–1459, Nov. 1991.

- J. R. Phillips and J. K. White, “A precorrected-FFT method for electrostatic analysis of complicated 3-D structures,” IEEE Trans. on CAD, vol. 16, no. 10, pp. 1059–1072, Oct. 1997.

- Z. Zhu, B. Song, and J. K. White, “Algorithms in FastImp: A fast and wideband impedance extraction program for complicated 3-D geometries,” in Proc. 40th Design Automation Conf., 2003, pp. 712–717.

- Momentum – ADS 2009, Agilent Technologies, 2009,

http://edocs.soco.agilent.com/display/ads2009/Momentum. - “Q3D extractor,” Ansys, Inc., 2009, http://www.ansoft.com/products/si/q3d extractor.

- W. Chai, D. Jiao, and C.-K. Koh, “A direct integral-equation solver of linear complexity for large-scale 3d capacitance and impedance extraction,” in Proc. 46th Design Automation Conf., 2009, pp. 752–757.

- S. Kapur and D. E. Long, “Large-scale full-wave simulation,” in Proc. 41st Design Automation Conf., 2004, pp. 806–809.

- iRCX Unified Technology File Format Usage, TSMC, 2008, version 1.4.

- T-N65-CL-SP-009-I1 65nm iRCX file at http://online.tsmc.com, TSMC, 2008.

- T. Imai, “A topology-oriented algorithm for the Voronoi diagram of polygons,” in Proc. 8th Canadian Conference on Computational Geometry, 1996, pp. 107–112.

- S. Kapur and D. E. Long, “Modeling of Integrated RF Passive Devices,” IEEE Custom Integrated Circuits Conference 2010.

(訳)

フィールドエンジニアリング&サービス本部 カスタムIC&シミュレーション&SPB

菅谷 英彦

Latest Issue

- 検証作業における人工知能との新しい協力関係

- 編集後記

- 安全性とセキュリティを考慮したプレシリコンでのコンカレント・ソフトウェア開発と検証

- Virtuosoプラットフォーム、最新バージョン20.1をリリース

- AWR Design Environmentを活用した増幅器設計

- 集積型RFパッシブ・デバイスのモデリングについての考察 EMX Planar 3D Simulatorの紹介(後編)

- Cadence OrbitIO - 2.5D/3DICソリューション

- Sigrity2019 Hotfix002アップデートのご紹介

- デジタル設計・サインオフ関連webinarのビデオをCadence Online Support (COS) 上でオンデマンド配信しています!

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues