Chiplet接続 標準規格UCIeとCadence UCIe IPのご紹介

みなさん、こんにちは。今回はCadenceのchiplet向けIP Solutionを紹介させて頂きます。CadenceではUltraLink D2D IPというchiplet向けIPを2019年より提供させて頂いており、多くのお客様にご採用頂いています。データレートは20~40Gpbs、低Latency、低電力なIPであり、chiplet向けIPとしてご好評を頂いております。 一方、2022年2月に、chipletの接続仕様を定義する標準規格「UCIe(Universal chiplet Interconnect Express)」が発表されました。UCIe 1.0では、Die間のI/O物理層やプロトコル、ソフトウェアスタックモデル等の仕様が定義されており、メーカー各社が他社製のDieを用いたchipletを実現することが可能となりました。 chipletは以下のように様々なメリットがあり、標準規格も定義されたことで、現在高い注目を集めています。

- 大きなDie サイズに対して、複数の小規模Dieを使用する事によるyield改善

- コスト削減、開発期間短縮、過去に設計したDieのリユース(異なるプロセスノードも可)

- 様々な機能や機能の数の実装が可能となり、Market Segmentation毎の開発が可能

UCIe規格とは

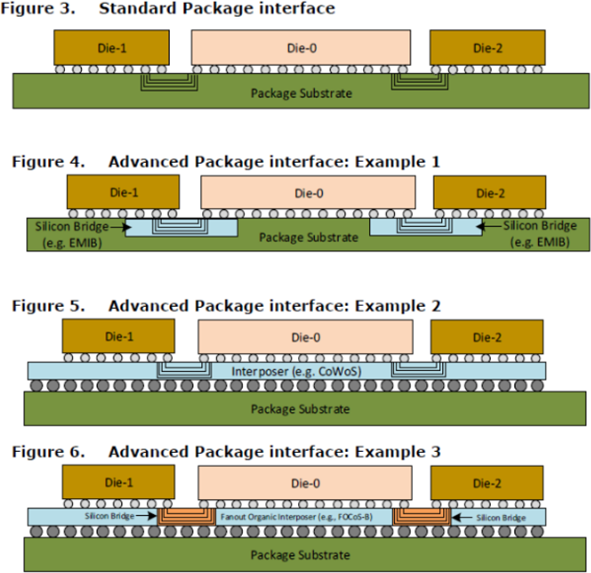

UCIeでは「Standard Package」と「Advanced Package」の2つが用意されています。

Standard PackageはLow cost、long reachをTargetとしており、有機パッケージ/サブストレートでのTraceを用います。Advanced Packageはhigh bandwidth、Low latency、short ReachをTargetとしたPerformance重視の仕様となります。

Figure 1 Example of UCIe Standard Package/ Advanced Package

*Images are credited to UCIe™ — Universal Chiplet Interconnect Express™

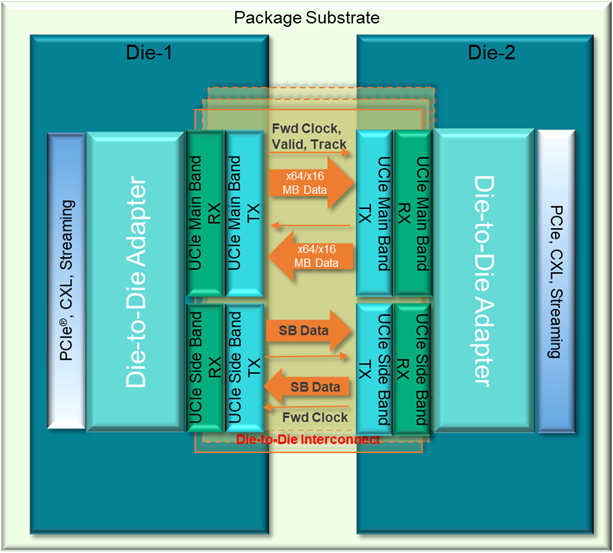

UCIeは以下の3つのLayer構造になっています。

- Physical Layer:

Electrical signaling, Clocking, Link trainingなどの機能を持ちます。 - Die-to-Die Adapter:

Link state management や 接続先とのParameter negotiationなどを行います。 - Protocol Layer

PCIeとCXLのサポートがあります。これらのプロトコルを使うことで、ユーザーアプリケーションは使い慣れたPCIe/CXL Protocolを用いてchipletを構築できます。その他のProtocolに対応するため、UCIeではStreaming protocolも定義されています。

Cadence UCIe IPのご紹介

CadenceではUCIe IP としてStandard Package、Advanced Packageの両方をサポートし、ファウンドリ各社の各プロセスノードでの準備がございます。また前述のUltraLink D2D IPからの拡張でUCIe IPを開発していることから、ファウンドリ各社の各プロセスノードでの実機評価済の多数の要素技術をUCIe IPに取り込んでおり、高いIP品質を実現しています。

Cadence UCIe IPは、高いbandwidth, low-power そしてlow-latencyを実現しており、Streaming, PCIe, CXL Protocolをサポートしています(Figure 2)。

Figure 2 Overview for Cadence UCIe IP

Cadence UCIe IPのKey Benefitsを紹介します。

- Standard packageとAdvanced packageの両方をサポート

- Advancedアーキテクチャー(*1)によるUltra-low powerの実現

- Lowest latency

- Maximum Die-to-Die throughput and link data integrity

- PCIe, CXL, Streaming protocolをすべてサポート

- Known Good Die(KGD)やロバストなテスト機能実装によるlink reliabilityの実現

(*1) Mixtured SerDes and DDRアーキテクチャー

Cadence Design IPは、今回ご紹介したUCIeだけでなく、最先端規格に対するIPラインナップを取り揃えております。今後もお客様のSoC開発課題の解決ができるよう取り組んでまいります。ご興味のある方は弊社営業までお問い合わせください。

今回紹介させていただいたIPについてはこちらをご覧ください。

Cadence chiplet and D2D Connectivity IPのご紹介:

https://www.cadence.com/en_US/home/tools/ip/design-ip/chiplet-and-d2d-connectivity.html

設計IP

プリンシパル アプリケーション エンジニア

奥山 健

Latest Issue

- OpenEyeのご紹介 人類の健康増進に貢献するために

- 組込みシステムの低コスト化、及び開発効率を向上させるDual-OS環境 ~Xtensaのセキュリティ拡張を用いた実現~

- ケイデンスオンラインサポート (Cadence Online Support: COS)のご紹介

- トピックス:CadenceLIVE Japan開催のご案内

- HiFi-TURB プロジェクト - AIおよび機械学習による乱流モデリング

- 「Celsius EC Solver」および「DataCenter Design Software and DataCenter Insight Platform」新機能のご紹介

- 新たな検証課題と高性能FastSPICEシミュレータSpectre FX

- PPA向上および短TAT化にも貢献! Digital Full Flowに融合したModus DFT Test Solutionのご紹介

- アサーション(SVA)の下書きをしたいときには

- OrCAD 便利機能のご紹介

- AI/MLアプリケーションの普及に対応しつつ一段と高速化が進むDRAMメモリーインターフェース

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues