AI/MLアプリケーションの普及に対応しつつ一段と高速化が進むDRAMメモリーインターフェース

近年、AIが様々なアプリケーションで利用されるようになり、多くの半導体にもAIアクセラレータが搭載されるようになってきました。AIアクセラレータを搭載した多くの半導体はすでに数多く開発されてきており、スマートフォン、AIスピーカー、センサー、自動運転、ドローンなどの分野で利用されています。AIアクセラレータは、AIタスクを専用に処理するための特殊なハードウェアで、CPUと比べて高速かつ低消費電力で動作するため、今後もAIアクセラレータはますます普及することが予想されています。

一方、AIアクセラレータでは、通常のCPUが必要とするメモリーインターフェースよりも高速なメモリーインターフェースが必要とされるケースが多くあります。AIアプリケーションやMLの処理は同時に多数のデータを処理する必要があり、高速かつ大容量のメモリーアクセスが必要となるためです。

ケイデンスでは、高速なDRAMインターフェースとして、LPDDR5、GDDR6、DDR5インターフェースを提供していますが、中でもLPDDR5メモリとGDDR6メモリのアプリケーションの多くはAI/MLとなっており、特にGDDR6のアプリケーションのほとんどがAI/MLとなっています。

DRAMメモリーベンダーではこれらの市場要求に対応するべくメモリーデバイスの高速化を進めており、ケイデンスもIPベンダーとしてこれらメモリーデバイスの高速化に追随して、IPの高速化を進めています。ここでは、最新のGDDR6 IPとLPDDR5 IPについて簡単にご紹介します。

1. TSMC N5で業界トップのパフォーマンス、シリコンで実証済みの22Gbps GDDR6 IP

ケイデンスではかねてよりTSMC N7/N6プロセス向けに16Gbps GDDR6 IPを提供してきましたが、昨年2022年末に、22Gbps GDDR6 IPを発表しました。22Gbpsで動作するGDDR6用IPは、最新世代規格のDDR5やLPDDR5に対して2倍以上のデータ速度を提供し、Cadenceの以前の 16Gbps GDDR6 IPよりも37%高速化されています。

アーキテクチャの改善により、動作条件の全範囲にわたって、ピンあたり最大 22Gbit/秒の帯域幅 (チップあたり 704Gbit/秒)が可能になり、動作電力とアイドル電力が低くなり、ビット誤り率 (BER) が低くなり、信頼性が向上しています。

このGDDR6 IPはTSMCのN5プロセステクノロジーでシリコン実証が完了しており、またこのIPソリューションはPHY、コントローラー、および検証IP(VIP)で構成されていますので、ユーザー様のチップ設計において開発を迅速化しリスクを軽減できます。

この22Gbps GDDR6 IPにより、AI/MLチップや、またハイパースケールコンピューティング、5G通信、自動車および民生用などの、非常に高帯域幅が必要とされるメモリアプリケーションの更なる高速化要求に応えていけるものと考えています。

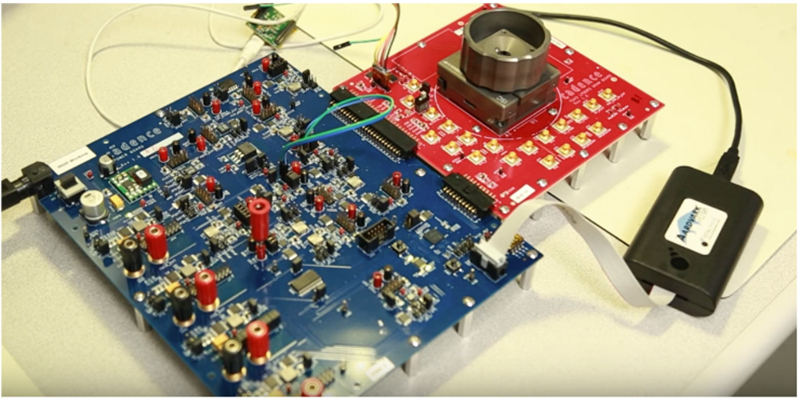

GDDR6テストボード

2. 9600MbpsのSK hynixの最高速度LPDDR5TモバイルDRAMとのインタ―オペラビリティを実証

LPDDR5 IPについて、ケイデンスでは8533Mbpsで動作するLPDDR5X IPを業界に先駆けて発表していました。今回更に高速なソリューションとして、SKハイニックスのLPDDR5T (Turbo)モバイルDRAMとケイデンスLPDDR5 IPのインターオペラビリティが発表されました。

SKハイニックスによるLPDDR5T(Turbo)モバイルDRAMは、データレートが8533MbpsのLPDDR5メモリよりも13%速い9600Mbpsを実現するとされています。このSKハイニックスの発表に引き続いて、ケイデンスではSKハイニックスのLPDDR5T(Turbo)モバイルDRAMとケイデンスLPDDR5 IPが、9600Mbpsで相互互換性をシリコン実証できたことを発表しています。

この発表についてSK ハイニックスの DRAM 製品企画担当副社長、Sungsoo Ryu 氏は次のように述べています。「SK ハイニックスの LPDDR5 ターボ モバイル DRAMは、スマートフォンを超えて、AI、機械学習、拡張/仮想現実など、新たな可能性を開きます。ケイデンスのメモリーインターフェースIPとの相互運用性を証明することは、顧客が9600Mbpsの動作を目標にできるようにするための重要なステップです。

このケイデンスのLPDDR5 PHY IPは、従来のケイデンスHS (High-Speed) PHYのアーキテクチャとGDDR6 PHYのアーキテクチャをベースにした、新しいPHYアーキテクチャを採用しており、最新の信号ブースト技術など新しい設計技術を実装し、高速化と低消費電力化を更に推し進めています。その結果SKハイニックスの9600Mbps モバイル DRAMと相互動作させた場合でも、大きなシステムマージンを備えた広いデータアイを実証できています。

LPDDR5X テストテストボード

これらの最新のケイデンスのメモリーインターフェースについては、例年7月に開催されているCadenceLIVE Japanにおいてセッションとデモブースで紹介をさせていただく予定でいます。近々CadenceLIVE Japanの開催のご案内がされましたら是非お運びいただき、シリコン実証のデモを含めてご覧いただけますと幸いです。ご一読いただき有難うございました。

設計IP

シニアAEマネージャ

伊原 誠

Latest Issue

- OpenEyeのご紹介 人類の健康増進に貢献するために

- 組込みシステムの低コスト化、及び開発効率を向上させるDual-OS環境 ~Xtensaのセキュリティ拡張を用いた実現~

- ケイデンスオンラインサポート (Cadence Online Support: COS)のご紹介

- トピックス:CadenceLIVE Japan開催のご案内

- HiFi-TURB プロジェクト - AIおよび機械学習による乱流モデリング

- 「Celsius EC Solver」および「DataCenter Design Software and DataCenter Insight Platform」新機能のご紹介

- 新たな検証課題と高性能FastSPICEシミュレータSpectre FX

- PPA向上および短TAT化にも貢献! Digital Full Flowに融合したModus DFT Test Solutionのご紹介

- アサーション(SVA)の下書きをしたいときには

- OrCAD 便利機能のご紹介

- Chiplet接続 標準規格UCIeとCadence UCIe IPのご紹介

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues