PPA向上および短TAT化にも貢献!

Digital Full Flowに融合したModus DFT Test Solutionのご紹介

LSI開発において高信頼で低価格のLSIを供給することは大切です。また、特定のアプリケーションに用いられるLSIにおいては、LSI出荷時のテストだけでなくFieldでのテストも重要になります。それを実現するためには、高機能で効率的なDFTを搭載する必要があります。Cadence®のModus DFT Test Solution(以下、Modus)では、大規模から小規模、高信頼からコスト重視のLSIなど様々なニーズに合わせて広範囲かつ柔軟なサポートが可能です。

一方、更に複雑化・大規模化するLSI設計では常にターゲットのPPAを満たした上で、設計の短TAT化が求められており、本来のLSIの機能に付加的に搭載されるDFTにより、これらに影響を及ぼすことは避けたいと言うのが実情ではないでしょうか?LSIの設計環境を広範囲に提供できるCadenceでは、Digital Full FlowとModusを融合させ、PPA向上と設計の短TAT化を実現することが可能です。

以下に、Modusがサポートする各DFT機能とPPA向上について紹介します。

Modus overview

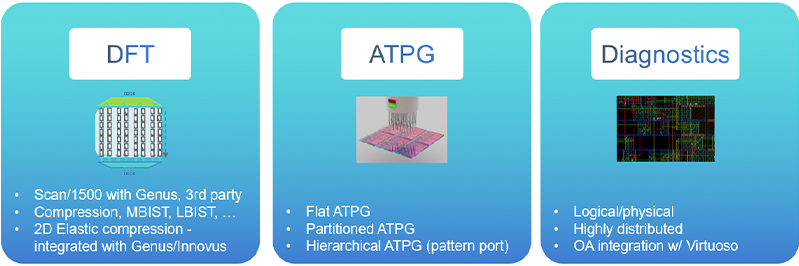

Modusは2016に発表以降、世界中の様々お客様で使用され、多くのシリコンテストでの実績があり、テスト回路挿入(DFT)、パターン生成(ATPG)、不良解析(Diagnostics)の工程をサポートしています。また、各分野での最高ツールである物理レイアウト(Innovus™)およびRTL・システムレベル検証(Jasper™/Xcelium™/Palladium®)と緊密に統合されています。

Physical-Aware DFT

物理配置を考慮したDFT機能について紹介します。

Modus Innovation: 2D Elastic Compression

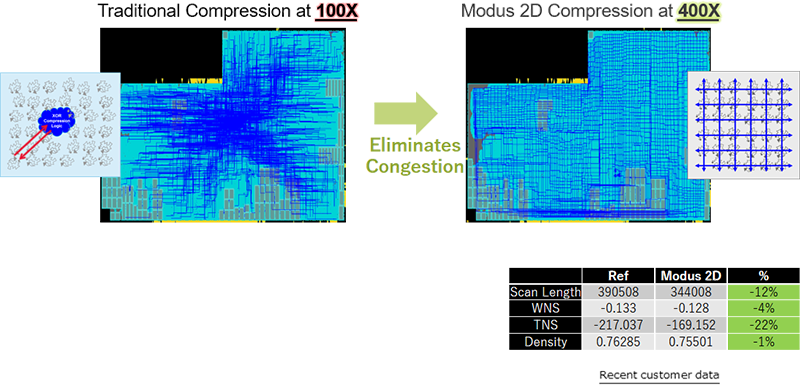

SCANの圧縮機能では、高い圧縮率においてもCoverage低下を抑えパターン長を効率的に削減することが重要です。一方、高圧縮時はレイアウト上の配線容量が増えてCHIP上の配線リソースを多く使用することになり、PPA悪化やダイサイズの拡大を招くことがあります。2DElastic Compression はチップのフロアプラン全体にフィジカルアウェアな2次元のグリッド構造を持つXOR Compression の論理を形成することにより、この問題を解決できます。

詳細については、過去の記事(こちら)を参照ください。

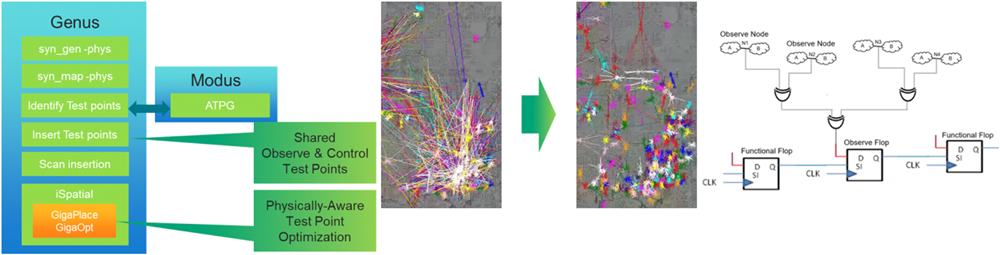

Physically Aware Test Points-Modus&iSpatial

SCANのCoverage向上およびパターン長の削減にはTest pointの挿入が有効ですが、大量に挿入することでエリアへの影響が大きくなります。これを防ぐために、複数のtest pointに対してFFを共有することで影響を少なくすることができます。しかしながら、配置的に離れたtest pointを共有することは、レイアウトの配線混雑を引き起こし、PPA悪化を招くことになります。Modusでは、Genus iSpatial flowの中で配置を考慮して近くのtest pointを共有し、配線混雑を防ぐことが可能です。

Main DFT Features

その他、Modusでサポートされる主なDFT機能について紹介します。

Low-Power Scan Shift & Unified Compression&LBIST(Logic BIST)

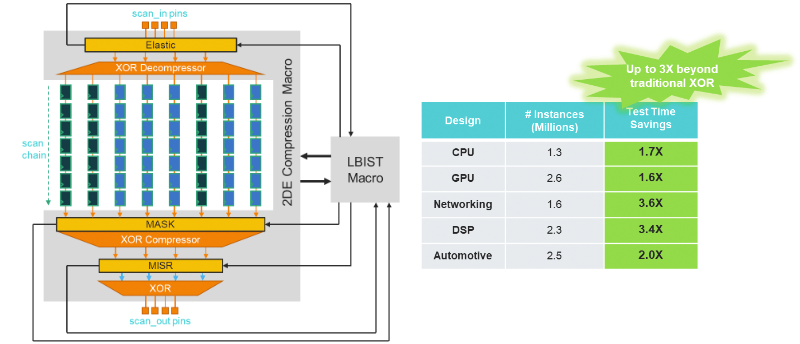

ModusのSCANでは圧縮回路にElastic Decompressorを使用することで、通常のXOR方式に比べて、3倍程度のテスト時間削減(テストパターンの削減)効果が可能となります。また、ATEで問題となるIR-Dropの対策として、パターン制御によるデータのトグル率の制御だけでなく、ハード的にScan Chainのトグルを制御することによりLow-power SCANを実現します。通常のSCANで用いられる圧縮回路はUnified CompressionマクロとしてLBIST時にも共有して使用することで回路エリアの削減が可能となっています。

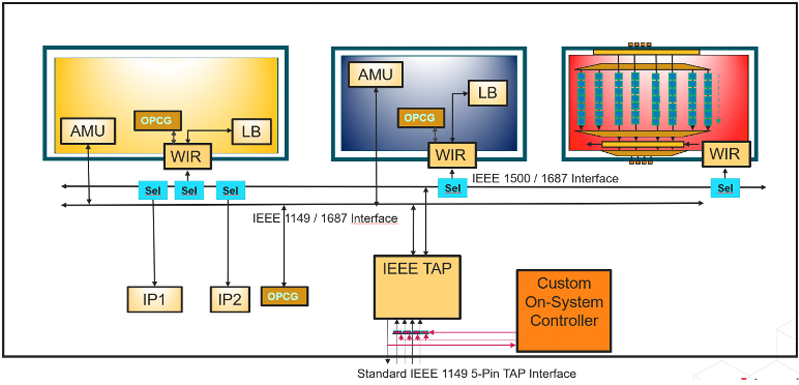

Hierarchical Test

大規模案件で必要となるHierarchical Testでは、TOPのSCAN-IN/OUTのportを構成と各CoreやSubsystemのSCANのport数に対して柔軟な割当が可能です。回路インプリ時には、オートマティックにCoreのインサーションを行い、制御方法としてIEEE1500/1687のinterfaceをサポートしています。また、パターンについては、Core/Subsystem/TOPのそれぞれのレベルのパターンをTOPに効率的にマイグレート可能です。

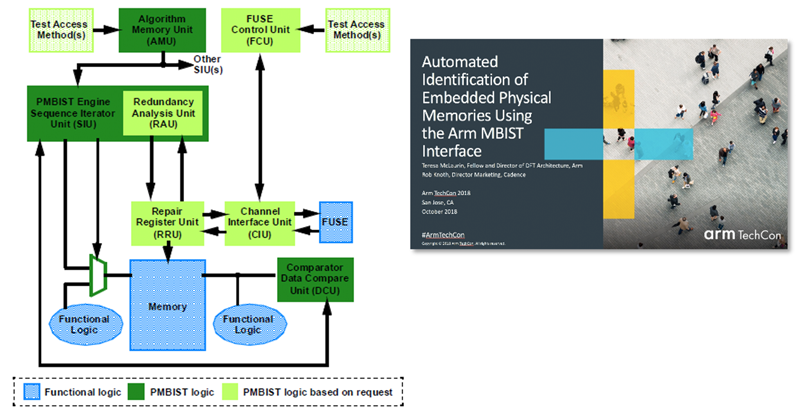

PMBIST (Programmable Memory BIST

PMBISTは、RTLおよびgateでのDFT挿入に対応しています。MemoryのRepairに関しては、NVM内に救済情報を保持するHard Repair、NVMを用いずRegisterを用いたsoft Repairの対応が可能です。また、テクノロジに応じた高信頼のパターンテストが用意されており、これらを使用することで高信頼のテストを実現できます。もちろん、User独自のパターンをプログラマブルに搭載することも可能となっています。PMBISTの特徴としては、構成に応じて最適な回路構成を構築し小さいエリアでの実装が可能、また、回路実装後にGUI Schedulerを用いた柔軟なパターンのスケジューリングが可能となっています。

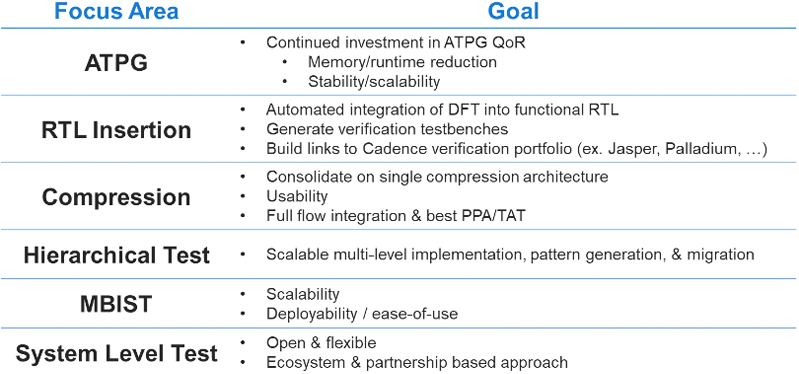

Modus Focus Areas

Modusの開発としてフォーカスしている領域を以下に示します。今回紹介させて頂いた主なDFT機能について更に機能/性能/ユーザビリティの改善もちろんのこと、RTL InsertionやSystem Level Testなどについても積極的に開発を進めています。ご期待頂ければと思います。

最後に

今回は、Modusの機能や特徴について簡単に紹介させて頂きました。全てのツールに当てはまることになると思いますが、特にDFTにおいては新しいツールを導入するのには抵抗があるとのお話を良く聞きます。Cadenceでは、他のツール同様にModusにおいても各DFTの機能や運用ケースごとに充実したRAK (Rapid Adoption Kits) が用意されており、非常に導入し易くなっています。是非とも、導入のご検討頂ければと思います。

フィールドエンジニアリング&サービス本部

デジタル&サインオフ

阿部 英明

Latest Issue

- OpenEyeのご紹介 人類の健康増進に貢献するために

- 組込みシステムの低コスト化、及び開発効率を向上させるDual-OS環境 ~Xtensaのセキュリティ拡張を用いた実現~

- ケイデンスオンラインサポート (Cadence Online Support: COS)のご紹介

- トピックス:CadenceLIVE Japan開催のご案内

- HiFi-TURB プロジェクト - AIおよび機械学習による乱流モデリング

- 「Celsius EC Solver」および「DataCenter Design Software and DataCenter Insight Platform」新機能のご紹介

- 新たな検証課題と高性能FastSPICEシミュレータSpectre FX

- アサーション(SVA)の下書きをしたいときには

- OrCAD 便利機能のご紹介

- AI/MLアプリケーションの普及に対応しつつ一段と高速化が進むDRAMメモリーインターフェース

- Chiplet接続 標準規格UCIeとCadence UCIe IPのご紹介

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues