Overview

Best-in-class PIPE PHY Verification IP for your IP, SoC and, system-level design testing.

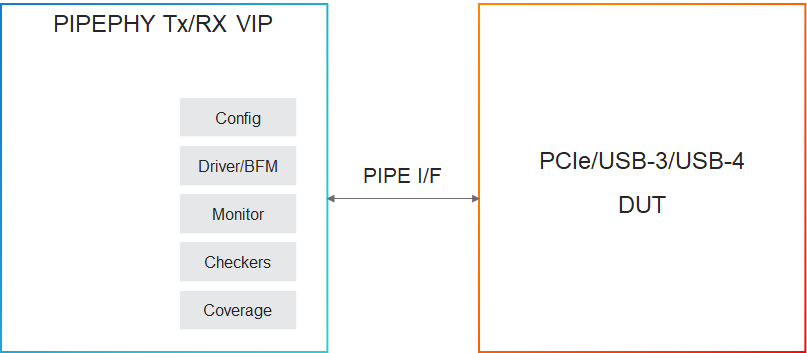

The Cadence® PIPE PHY Verification IP (VIP) provides a mature, highly capable verification solution for the PHY layer of complex protocols such as PCIe 3/4/5, USB-3.x, USB-4, DisplayPort and SATA at the Intel PIPE (PHY Interface for PCI Express*, SAA, USB-3, DisplayPort, and Converged IO Architectures). The VIP supports simulation platform and enables metric-driven verification of IP and System on Chip (SoC) designs against PIPE PHY protocol specifications. PIPE PHY VIP is compatible with the industry-standard Universal Verification Methodology (UVM) and supports all leading simulators.

Supported Specifications: Intel PIPE version 4.3, 4.4,1 and 5.2 specifications.

Product Highlights

Key Features

The following table describes key features from the specifications that are implemented in the VIP:

Feature Name |

Description |

|---|---|

Device Type |

|

PHY Architecture |

|

Pin Interface |

|

Protocols Mode |

|

Simulation Test Suite

Extensive testsuite, coverage model, and verification plan with clear linkage to the specification for simple and fast compliance testing.

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles