Overview

Best-in-class SPI Verification IP for your IP, SoC, and system-level design testing.

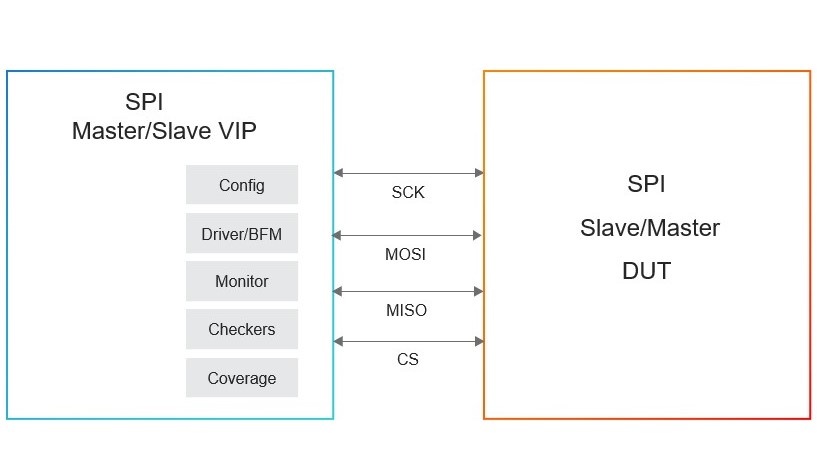

This Cadence® Verification IP (VIP) provides support for the SPI protocol. The SPI VIP provides a complete bus functional model (BFM) and integrated automatic protocol checks. Designed for easy integration in testbenches at IP, system-on-chip (SoC), and system levels, the Cadence SPI VIP helps you reduce time to test, accelerate verification closure, and ensure end-product quality. Cadence VIPs run on all major simulators and supports the SystemVerilog verification language along with associated methodologies, including the Universal Verification Methodology (UVM) and Open Verification Methodology (OVM).

Supported Specifications: Samsung SPI based on the Exynos 5250 spec Revision 1.00, Motorola SPI based on Block Guide V03.06 and SafeSPI SPI for Automotive Safety V0.15.

Product Highlights

Key Features

The following table describes key features from the specifications that are implemented in the VIP:

Feature Name |

Description |

|---|---|

Full Duplex |

|

Variable Size Shift Registers |

|

Variable Bus Sizes |

|

Tx and Rx FIFOs |

|

Simulation Test Suite

VIP comes along with a testsuite of scenarios for easy VIP evaluation and deployment.

Please contact us for further information.

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles