Overview

Gold standard for JEDEC® UFS memory device for your IP, SoC, and system-level design verification.

In production since 2012 on multiple production designs.

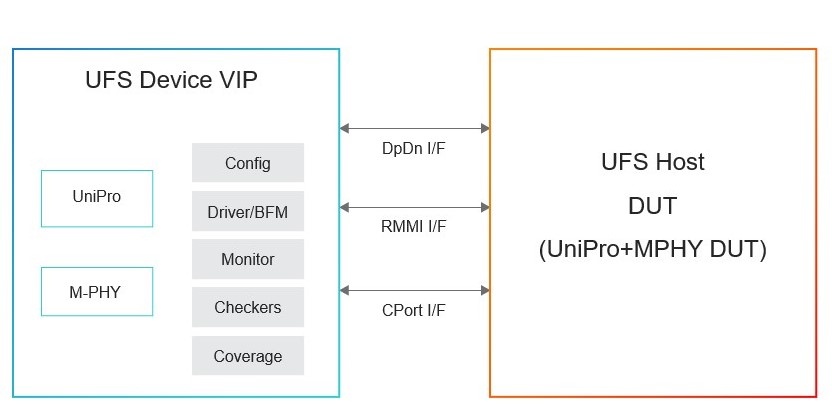

This Cadence® Verification IP (VIP) supports the JEDEC Universal Flash Storage (UFS) standard. The VIP for UFS is compatible with the industry-standard Universal Verification Methodology (UVM), runs on all leading simulators, and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model.

Product Highlights

Key Features

The following table describes key features from the specifications that are implemented in the VIP:

Feature Name |

Description |

|---|---|

Interfaces |

|

UTP Layer - UPIUs |

|

UCS Layer - SCSI Commands |

|

UFS Protocol Features |

|

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles