Overview

Best in class MIPI® I3Csm Verification IP for your IP, SoC, and system-level design testing.

In production since 2015 on dozens of production design.

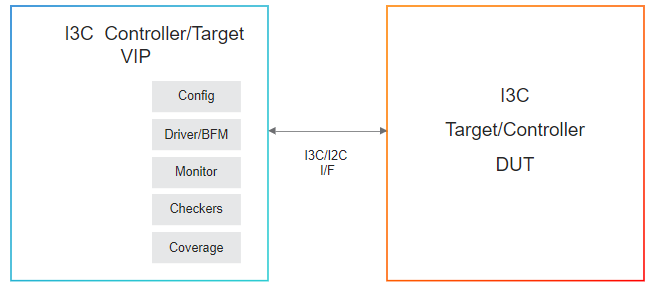

The Cadence® Verification IP (VIP) for MIPI® I3Csm VIP provides support for the MIPI I3C protocol specification. It provides a mature, highly capable compliance verification solution that supports simulation, protocol checking, coverage collection, and analysis, making it applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification. The VIP for I3C helps you reduce time to test, accelerate verification closure, and ensure end-product quality. The VIP runs on all major simulators and supports SystemVerilog and e verification languages along with associated methodologies, including the Universal Verification Methodology (UVM) and Open Verification Methodology (OVM).

Product Highlights

Key Features

The following table describes key features from the specifications that are implemented in the VIP:

Feature Name |

Description |

|---|---|

I3C SDR Mode |

|

I3C HDR-DDR Mode |

|

I3C HDR-Ternary Modes |

|

I2C Legacy Mode |

|

I3C CCC |

|

Simulation Test Suite

Extensive testsuite, coverage model, and verification plan with clear linkage to the specification for simple and fast compliance testing.

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles