Overview

Gold standard for JEDEC® xSPI memory device for your IP, SoC, and system-level design verification.

xSPI in production since 2019 for many production designs.

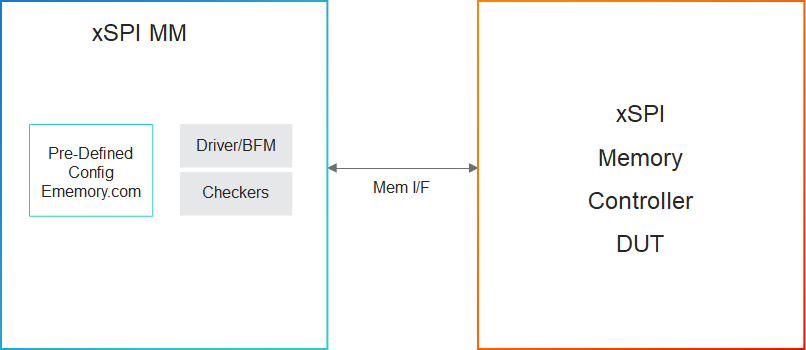

The Cadence® Memory Model Verification IP (VIP) for xSPI provides verification of xSPI (Expanded SPI) NOR flash devices using the SPI protocol. The VIP for xSPI is compatible with the industry-standard Universal Verification Methodology (UVM), runs on all leading simulators, and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model. The VIP for xSPI includes both support for xSPI and VIP for OSPI NOR.

Supported specification: JEDEC specifications: JESD251 Profile 1 v1.0, JESD251-A1, JESD252, and JESD216D and Memory Vendors specifications of ADESTO (DS_XP032_114G_122018), MICRON (tn1235_sfdp_mt35x Rev. B 10/18 EN - compliant to JESD216B ONLY), MACRONIX, (AN0726 Rev1 for MX66UM2G45G) and CYPRESS (002-18216, Rev:*M).

Product Highlights

Key Features

The following table describes key features from the specifications that are implemented in the VIP:

Feature Name |

Description |

|---|---|

xSPI Profile 1 |

|

Modes |

|

Reset |

|

Modes Switching Commands |

|

Master Your Tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles