Overview

Best-in-class MIPI® SoundWire-I3Ssm (SWI3S) Verification IP for your IP, SoC, and system-level design testing.

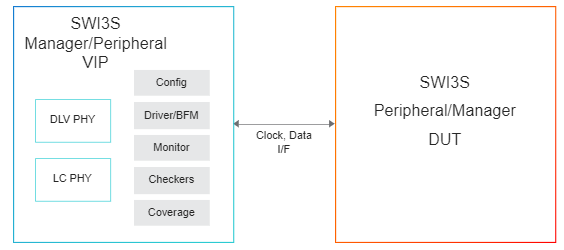

The Cadence Verification IP (VIP) for SoundWire-I3S (SWI3S) is designed for easy integration in test benches at the IP, system-on-chip (SoC), and system level. The VIP for SWI3S runs on all simulators and supports SystemVerilog along with the widely adopted Universal Verification Methodology (UVM). This enables verification teams to reduce the time spent on environment development and redirect it to cover a larger verification space, accelerate verification closure, and ensure end-product quality. It supports Manager, and a configurable number of peripherals (1-8).

Supported Specifications: MIPI SoundWire-I3S specification version 0.5r02, June 2022.

Product Highlights

Key Features

The following table describes key features from the specification that are implemented in the VIP for SWI3S:

Feature Name |

Sub-Feature Name | Description |

|---|---|---|

PHYs |

|

|

Interfaces |

|

|

Devices |

|

|

Link Control and Reset |

Sequences |

|

Resets |

|

Simulation Test Suite

SWI3S VIP has a testsuite of scenarios for easy VIP evaluation and deployment.

Master your tools

Tutorials, Documentation, and Local Experts

Cadence Online Support

Increase your efficiency in using Cadence Verification IP with online trainings, VIP Portal, application notes, and troubleshooting articles