UCIe™ PHY and Controller—To Die For

Read More

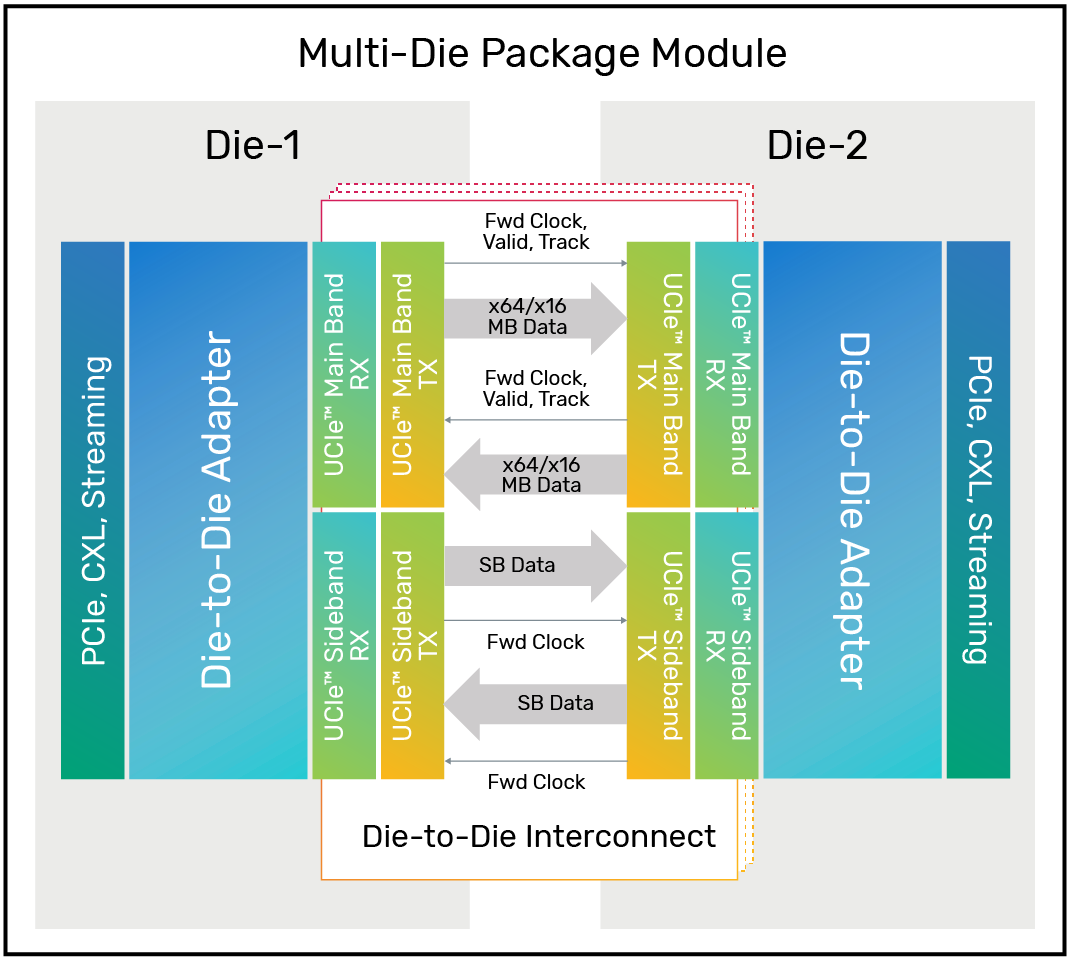

Cadence UCIe™ PHY 是一款高带宽、低功耗且低延迟的 die-to-die 解决方案,能够为高性能计算、AI/ML、5G、汽车和网络应用实现多晶粒系统的封装集成。UCIe™ 物理层包括链路初始化、训练、电源管理状态、通道映射、通道反转和加扰。UCIe™ 控制器包括 die-to-die 适配器层和协议层。适配器层通过链路状态管理以及协议和 flit 格式的参数协商来确保可靠传输。UCIe™ 架构支持多种标准协议,如 PCIe、CXL 和流式原始模式。

支持标准封装 (2D) 和高级封装 (2.5D)

采用先进架构,可满足超低功耗要求

适用于数据密集型应用

采用高效设计,可最大限度提高 die-to-die 吞吐量和链路数据完整性

支持 PCIe、CXL 和流式协议

采用 KGD 和稳健的测试方法,确保无缝链接的可靠性

UCIe™ 代表 Universal Chiplet Interconnect Express,这是一种 die-to-die (d2d) 串行互连。