概述

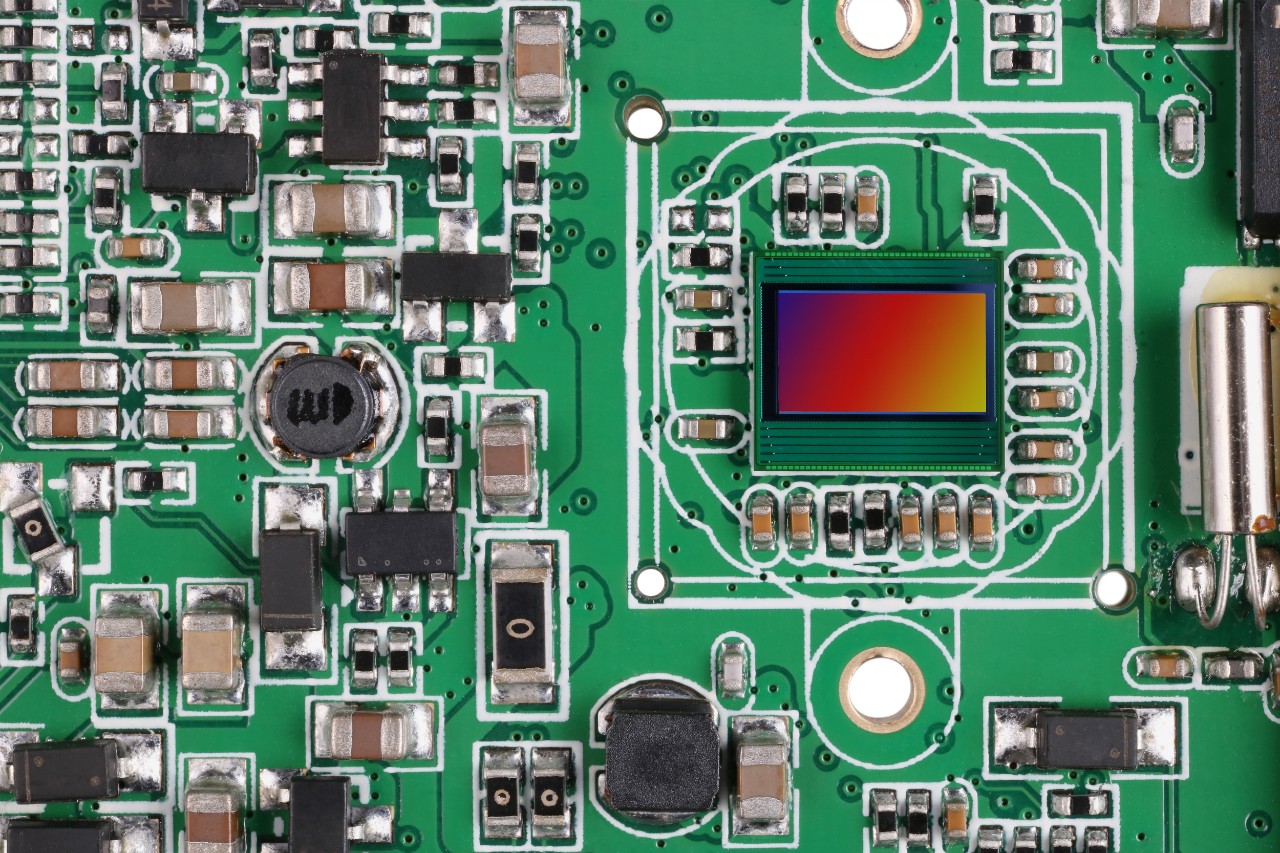

MIPI CSI-2 receiver

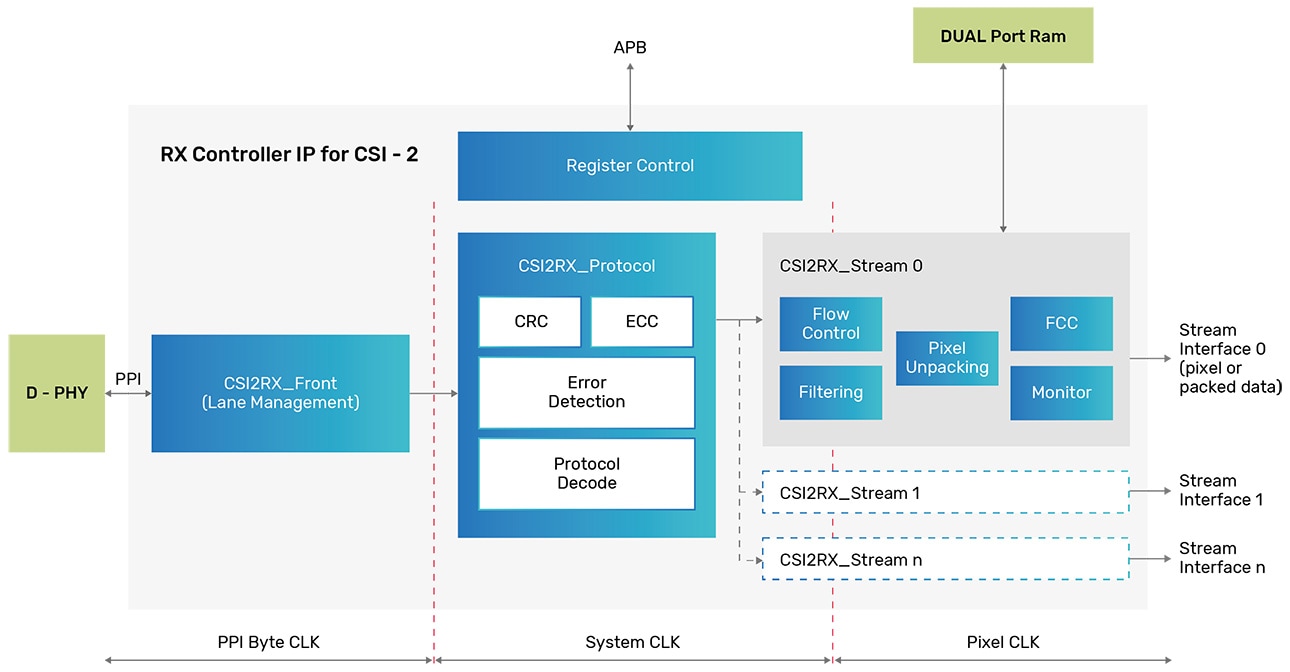

面向 MIPI® CSI-2sm 的 Cadence® Receiver (RX) IP 是一个经过完全验证、可配置的数字内核,符合 MIPI Alliance CSI-2 v2.1 规范。该控制器 IP 负责处理和解码基于 CSI-2 协议的摄像头或其他传感器数据流,并管理有效载荷数据转发或解包到像素流接口。非常适合在应用或图像处理器和符合 MIPI CSI-2 的相机传感器之间提供高速串行接口。

MIPI CSI-2 接收器框图

核心优势

主要功能