More Than Mooreデバイスに不可欠なチップレット間通信を実現するケイデンスのIPソリューション

ムーアの法則(Moore’s Law)に従った微細化は物理的に限界にきていると言われています。5nm辺りが限界と言われ続けていたものの、更なる微細化への戦略がシリコンファウンダリより発表されています。ムーアの法則に従った微細化による性能向上を目指す戦略 (More Moore) に対し、機能素子を融合して機能を追加する戦略(More Than Moore)へシフトする動きが大手半導体メーカーより見え始めています。More Than Mooreのデバイスは新しい機能の多様化を表しており、AI、5G、IoT、自動運転など拡大し続ける処理能力へのデマンドとニューラルセンサーといった新しいアプリケーションの融合により今後の劇的な拡大が期待されています。More Than Mooreデバイスを実現する方法として「チップレット」と呼ばれる複数のチップを組み合わせ、さらにパッケージ技術を駆使して1パッケージでシステムを作り上げる手法があります。小さなチップレットは大きな1チップに比べて格段に歩留まりが高く、チップレットごとに最適なプロセスで製造できる柔軟性があり、電力やチップの価格を抑えられるなどのメリットがあります。このようなメリットを持つMore Than Mooreデバイスの実現にはチップレット同士をうまくつなぎ合わせてリンクする技術が必要不可欠です。Cadenceにはチップレット間通信を実現するソリューションを提供する用意があります。

CadenceのIn-Package Interconnect Solution

Cadenceのチップレット間接続に対応するIP Solutionを紹介させていただきます。一つ目は112G-XSR PAM4 PHY IPです。Cadenceの112G-XSR IPソリューションは、クラウドデータセンターおよび光通信アプリケーションの開発を可能にするには重要な技術であるとともに、パッケージ内のチップ間接続を実現するために必要不可欠な技術です。IEEE標準規格の仕様に完全準拠するとともに、プログラマブルなDSPベースのアーキテクチャーにより、必要な伝送距離に対して最適な電源供給を行い、データ損失や雑音の多いチャネル状態においても優れたリカバリー機能を提供します。112G-XSR IPはMulti-lane化によりチップ間接続に要求される広帯域を満たしつつ、最適化された消費電力およびサイズによってより高密度なSystem-in-Package接続を提供できます。例えば32 Multi-laneにおいては3.6Tbps RX + 3.8Tbps TXの広帯域を実現可能です。以下は112G-XSR IPの特長となります。

Highlights

- TSMC N7プロセスにてシリコン実証済み

- 10dbまでの挿入損失に対応

- 112G 4パルス振幅変調(PAM4)および56G非ゼロ復帰(NRZ)モードに対応

Key Features

- X8 laneまでのconfigurationが可能

- DAC(D/A コンバーター)ベースのトランスミッタ有限インパルス応答(FIR)イコライゼーションのタップを実装

- イコライゼーションの複数の段階を持ったデジタル・シグナル・プロセッサ(DSP)を持つレシーバー

- ASICの介在無しに、完全に自律的な起動とadaptationの対応

- PRBS (pseudo random binary sequence) の生成およびチェック機能を持つ内蔵BIST (built-in self-test) に対応

2つ目のソリューションはUltraLink™ D2D IPです。クラウドコンピューティングアプリケーションに向けたお客様の先端SoCデザインの開発を支援するためのIPであり、高帯域、低レイテンシー、低消費電力を実現するために必要不可欠な技術となります。NRZシリアルインターフェースLine Rateは最大40Gbpsを実現し、最大1Tbps/mmの単方向帯域幅を提供できます。Bit Error Rate (BER) は1e-15を実現しており、そのため転送エラー訂正 (FEC) が不要となります。これにより低latency設計の容易性が期待できます。またはUltraLink D2D IPは有機基板上のマルチチップモジュールに対応することにより、シリコンインターポーザーを用いることなく高いコスト優位性を実現できます。以下はUltraLink D2D IPの特長となります。

Highlights

- TSMC N7プロセスにてシリコン実証済み

- 有機基板上のマルチチップモジュールに対応

- 最大40GbpsのLine Rateを達成し、1Tbps/mmの単方向帯域幅を実現

- BER 1e-15を実現

Key Features

- 20~40Gpbsに対応する柔軟なdata rate

- シングルエンドの非ゼロ復帰 (NRZ) シグナリング方式、およびレシーバーへの高速差動クロック出力方式

- PRBS (pseudo random binary sequence) の生成およびチェック機能を持つ内蔵BIST (built-in self-test) に対応

- 異なるテクノロジノードやファウンドリ間の相互接続が可能

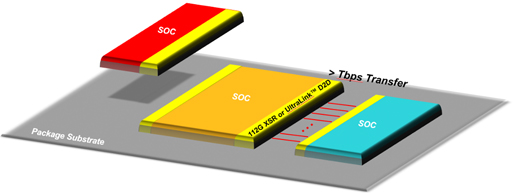

図1は112G-XSR PAM4 PHYおよびUltraLink D2D IPを用いたチップレット接続イメージとなります。CadenceのIPによりTbps (terabit per second) オーダーの超高速チップレット間通信を達成しつつ、チップレットごとに異なるプロセスでの製造を行うことで、コスト、電力のメリットを享受しつつ柔軟な機能を持つMore Than Mooreデバイスの実現が可能です。

図1 112G-XSR PAM4 PHYおよびUltraLink D2D IPを用いたチップレット接続イメージ

112G-XSR IPとUltraLink D2D IPの特長を比較したものが表1となります。各IPが持つ特長により、性能/消費電力/コストをメトリックとしたお客様独自のMore Than Mooreデバイス実現に大きく貢献できます。

| IP | Power | Latency | System Cost | Other |

|---|---|---|---|---|

| 112G-XSR | + | + | + | ++ Standard Ethernet compatible |

| UltraLink D2D | ++ Better power consumption |

++ Lower |

++ Cost advantage |

++ Line Rate flexible |

表1 112G-XSR IPとUltraLink D2D IPの比較

今回紹介させていただいたCadenceのコネクティビティIP Solutionについての詳細はこちらをご覧ください。

Cadence SerDes IPのご紹介:

https://ip.cadence.com/ipportfolio/ip-portfolio-overview/interface-ip/serdes-ip

Cadence UltraLink D2D IPのご紹介:

https://ip.cadence.com/ipportfolio/ip-portfolio-overview/interface-ip/serdes-ip/ultralink-d2d-phy-ip

https://ip.cadence.com/news/627/330/New-Cadence-UltraLink-D2D-PHY-IP-for-Die-to-Die-Connectivity-Enables-High-Performance-Applications-with-Cost-Effective-Packaging

Cadenceのチップ間接続に対応するIP SolutionはMore Than Mooreデバイスを実現するために必要不可欠な技術であり、Cadenceには最適なソリューションを提供する準備ができています。チップ間接続IPにご興味をお持ちのお客様は是非ともCadenceの担当営業までご連絡ください。

設計IP

村田 直也

Latest Issue

- Dynamic Duo 2.0と新製品Palladium Z2 およびProtium X2のご紹介

- 医療現場で期待されるハンズフリーソリューション

- ケイデンス・オンライントレーニングの無料アクセスのご案内

- 日本語ブログのご紹介

- Cadence Topics

- SOCのオンチップバス及びメモリサブシステムの性能検証を効率化するSystem VIP

- NUMECAの買収、NUMECA製品の紹介

- 拡張モバイルブロードバンド(eMBB)向けの新しい5G NR設計

- EMX Planar 3D Solver version 6.0アップデートとVirtuoso RF Solution環境から実行できる電磁界解析フロー

- SIGRITY/SYSANLS 2021.1の最新アップデート情報のご紹介

- プリント基板設計ツールAllegro/OrCAD:SPB17.4-2019 QIR2 最新機能改善と便利機能のご紹介

- SDC検証の包括ソリューションツールConformal Litmus誕生 〜 タイミング制約検証の新しい提案 〜

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues