プリント基板設計ツールAllegro/OrCAD:SPB17.4-2019 QIR2

最新機能改善と便利機能のご紹介

Allegro/OrCAD 17.4-2019の各プロダクトはファーストリリース以来、 QIR (Quarterly Incremental Release)を通して継続的な機能拡張を実施しています。 本稿では2020年6月リリースのQIR1から、最新の2021年1月リリースのQIR2までで新機能や改良点の一部をご紹介いたします。

Allegro® PCB Editor / OrCAD® PCB Editor

Dynamic Shape機能改良

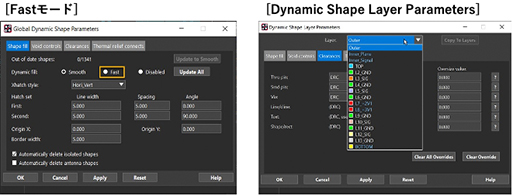

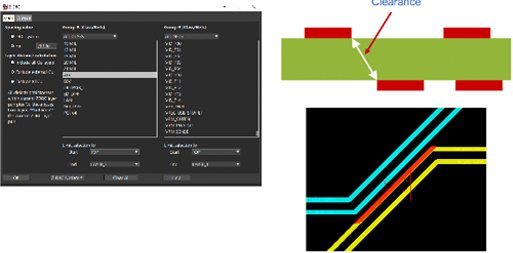

新しいDynamic Fillモード‘Fast’により、Dynamic Shapeのパフォーマンスが大幅に向上しています。‘Fast’モードはこれまでの‘Rough’モードを置き換えるものであり、Dynamic Shapeアップデートの遅れや遅延を排除し、アクティブなEtch編集中のパフォーマンスが大幅に向上しています。また、Shape Voidの結果は、Smooth Shapeのような接続性と外観を維持します。新しいダイアログ‘Dynamic Shape Layer Parameters’において、階層レベルまたは個々のレイヤーレベルでレイヤー固有のShapeパラメーターを定義する簡単な方法を提供します。

推奨される使用法:

1.まずGlobal Dynamic Shape Parametersでデザイン全体の設定

2.次にDynamic Shape Layer Parametersでレイヤー固有の設定

3.最後に必要な場合にのみInstance Parametersで個々のShape設定

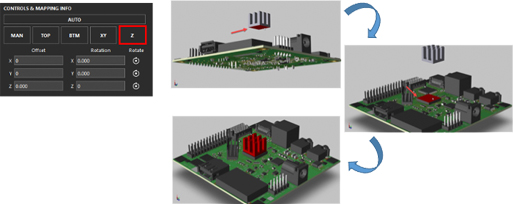

- 3D Canvasアップデート

STEPモデルのみをマッピングする既存のSTEP Package Mappingに変わり、新しいModel Mapper機能をサポートしました。このModel MapperではSTEPだけでなくSolidworks、Simens NX、Parasolid、Creoなどの様々なネイティブCADフォーマットを使用することができます。

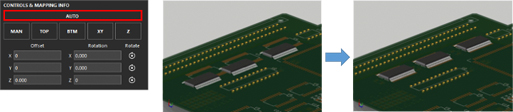

より詳細なモデルの使用による精度の向上を実現しつつ、3D Canvasへのロード時間も改善しています。ほとんどのモデルはボタン一つ(Auto機能)でマッピング可能ですが、以下のような様々な位置調整機能もサポートしています。

Model Mapper - Auto

AUTOボタンをクリックして、モデルをフットプリント(シンボル)に自動的に位置合わせ

Model Mapper -マニピュレータ・コントロール

3Dマニピュレータ・コントローラがモデル上に表示され、3方向に手動で移動

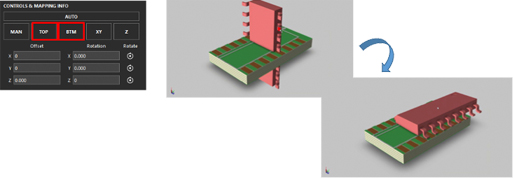

Model Mapper -インテリジェント・サイド機能

選択したモデルのフェースをPackageシンボルのTOPまたはBOTTOMに自動で位置合わせ

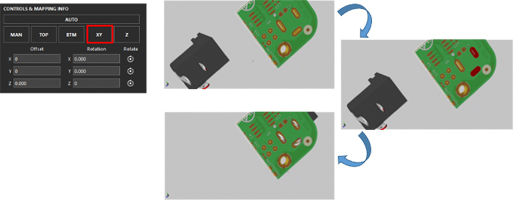

Model Mapper - XY機能

コネクタなどの複雑なコンポーネントを対象とし、最初にインテリジェント・サイド機能を実行し、次にXYを実行。

Model Mapper - Z 機能

モデルのフェースをZ方向の任意の位置に調整

例:ヒートシンクの下側をBGAチップの上側にマッピング

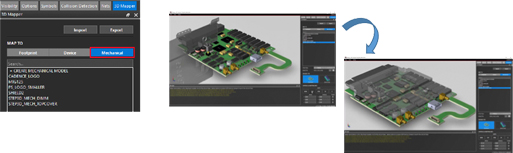

Model Mapper – メカニカル・モデル

メカニカル・モデル(ケース・ヒートシンク等)をPCBにマッピング

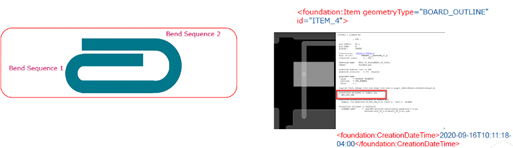

EDMD(IDX 4.0 )サポート

2020年6月にEDMD(ECAD/MCAD Collaboration)によって承認されたIDX(Incremental Design Exchange)スキーマのバージョン4.0をサポート。バージョン4.0の新機能と機能拡張にはベンド部の曲げ順序のサポート、プロパティではなく属性としてジオメトリの使用目的を定義することによる処理の高速化とファイルサイズの削減、プライマリ・ピン(ピン1、極性など)の識別、UTC Standardによるタイムスタンプの識別が含まれます。

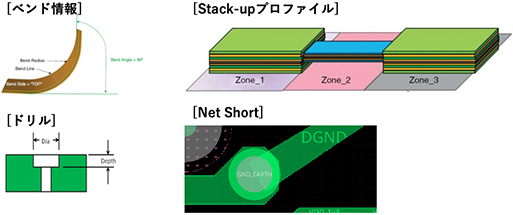

IPC2581 Revision Cサポート

IPC2581 Revision Cをサポートしました。Revision Cの新機能/機能拡張にはリジッドフレックス向けのベンド情報(ベンド角度、半径、方向、順序、ベンド領域)、領域ごとの材料や境界を含むStack-upプロファイルのサポート、新しいドリル機能(Counter sink/Counter bore)のサポート、ショートネットのネット名を識別、ジオメトリ用途の定義等が含まれます。

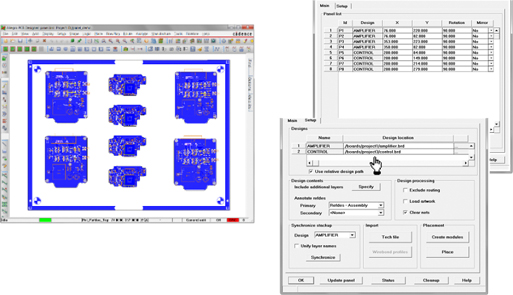

Z-DRCとPanelization

Productivity Toolbox Optionで提供されていたZ-DRCとPanelizationがAllegro PCB Designerの標準機能として利用可能になりました。

Z-DRC:QIR2(HotFix013)より利用可能

チェック対象オブジェクトはNetまたはNet Classベースで任意の組み合わせで指定可能であり、Z方向のクリアランスチェックを行いDRCエラーマーカーやオーバーラップ箇所のグラフィック表示を行います。

Panelization:HotFix008よりAllegro® PCB Designer / OrCAD® PCB Designer Professionalで利用可能

面付けに特化した機能であり、ボードは個別やアレイ毎に配置可能であり、個別に回転や反転も可能です。また、基となる基板にアップデートがあった場合の面付基板へのアップデートや異種基板もサポートします。

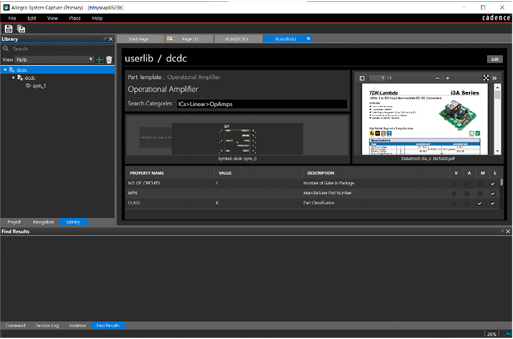

System Capture

Unified Library

System Captureでは、ライブラリとパーツを作成するための完全なツール内サポートも備えた新しいネイティブライブラリ形式がサポートされました。

System Captureで論理回路図デザインを作成できるだけでなく、ライブラリやパーツを作成および編集することもできます。

3つのライブラリモード

OrCAD Captureライブラリ、DE-HDLライブラリ、Unified Libraryと3つのライブラリモードがサポートされました。

ライブラリモード 使用ライブラリ 設定 OrCAD Captureライブラリ Capture OLB/CIS Capture.iniファイルが以下にある

%HOME%\cdssetup\OrCAD_Capture\17.4.0DE-HDLライブラリ DE-HDLライブラリ 環境変数CDS_SITEがある

%CDS_SITE%\cdssetup\cds.libを参照Unified Library Unified Library

(*.ldax)上記2項目が存在しない ※注意事項

capture.iniと%CDS_SITE%の両方が存在した場合は、OrCAD Captureライブラリモードになる。

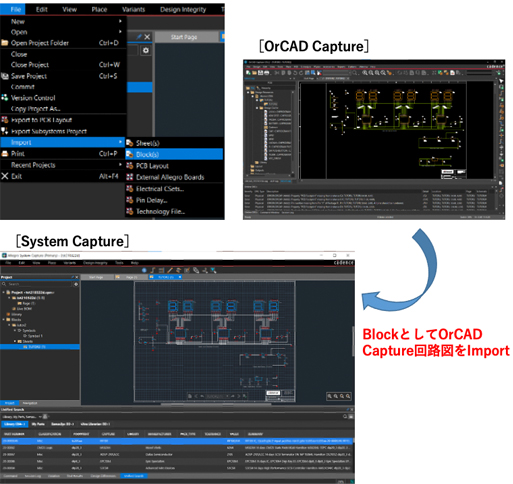

-%CDS_SITE%よりも%HOME%が優先されるためOrCAD Captureデザインインポート

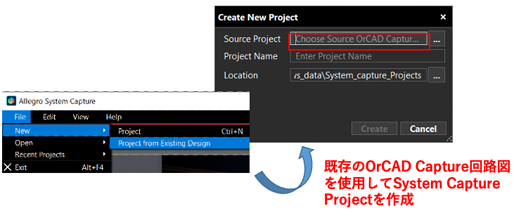

System CaptureからのOrCAD Captureライブラリ及びCIS DBへの直接ライブラリアクセスが強化されました。

OrCAD Captureデザインに基づくSystem Captureデザインを作成したり、OrCAD CaptureデザインをブロックとしてSystem Captureデザインにインポートしたり出来るようになりました。

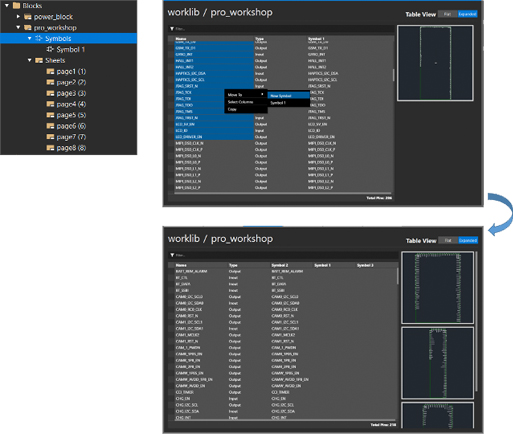

階層シンボルの分割

多ピンデザインの分割と分割パーツの配置をサポートしました。

このようなシンボルの目的は、回路シートに簡単に収まるようにシンボルサイズの変更が可能です。

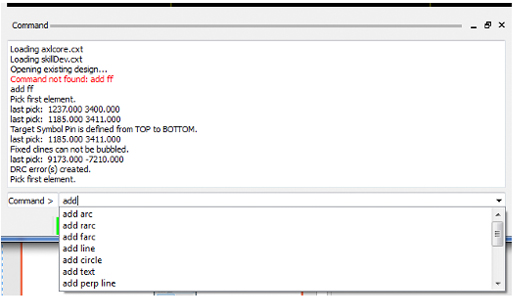

コマンド・ウィンドウ

コマンド入力時に有効なオート・コンプリート機能、使用履歴からのコマンド入力といった機能が追加され、キー入力でのコマンド実行をサポートします。

また、「Warning」はオレンジ、「Error」は赤とメッセージが強調されるように表示色が拡張され、重要なメッセージの視認性を向上しました。

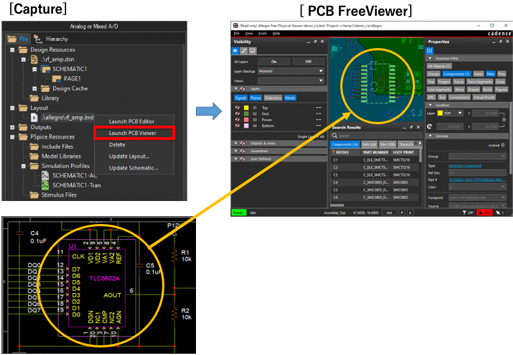

OrCAD® Capture PCBフローの使いやすさの向上

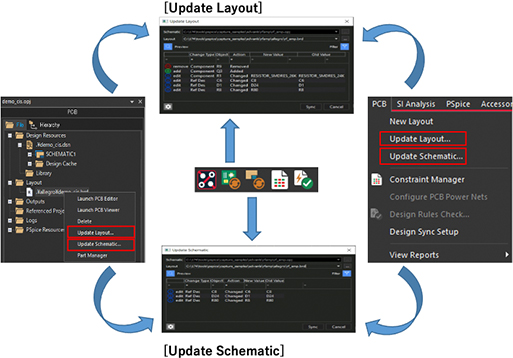

新しいデザイン同期オプション

デザイン同期コマンド「Design Sync」が「Update Layout」と「Update Schematic」二つに分割されることにより、同期コマンドの操作性が向上しました

また、プロジェクトマネージャーの[Layout]フォルダーの下にあるボードファイルを右クリックするポップメニューやPCBツールバーのアイコンからもアクセス可能です。

PCB FreeViewer

プロジェクトマネージャーの[Layout]フォルダーの下にあるボードファイルを右クリックするとポップメニューに「Launch PCB Viewer」が表示され、FreeViewerの起動が可能となり回路図とレイアウトのクロスプローブ機能をご活用いただけ易くなりました。

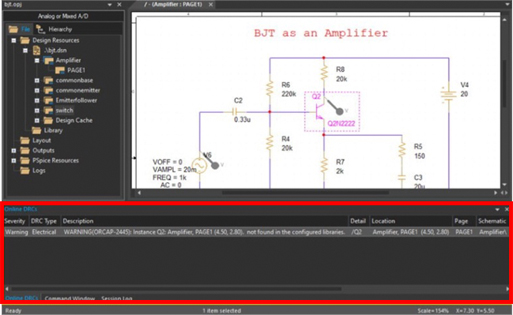

シミュレーション用デザインのダイナミックチェック

回路図にパーツを配置した際に、パーツに割り当てられているPSpiceモデルがライブラリファイルに見つからない場合、Online DRC タブ内にメッセージが表示されるようになりました。

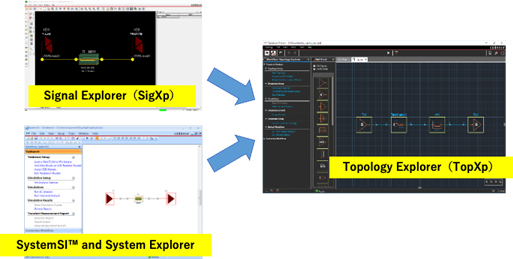

Topology Explorer(TopXp)

新しいトポロジーベースのSI解析環境

SPB17.4よりリリースされた、Cadence® System Captureキャンバスに基づきSignal Explorer(SigXp)とSigrity™ SystemSI™を操作性に優れたGUIで統合した新しいトポロジーベースのSI解析環境です。SigXpトポロジーファイル(.top)やSystemSI環境ファイル(.ssix)からの移行も、TopXpにロードするだけです。

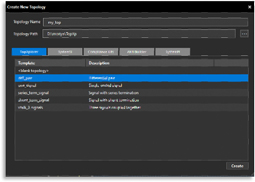

Topology Workbench

Topology Workbenchでは様々なワークフローをご用意しており、解析目的に合ったテンプレートを選択いただけます。

1.TopXplorer – プリレイアウトSI解析

2.SystemSI™ - DDRパラレルバス解析

3.SystemSI™ - 高速シリアルI/F 解析

4.Compliance Kits - 高速シリアルI/F 解析

5.AMI Builder – IBIS-AMIモデル作成

6.SystemPI – システムレベルPI解析

Sigrity Aurora とのインテグレーション

SPB17.4 QIR2より、Sigrity AuroraとTopXpのインテグレーションが拡張され、Allegro レイアウトキャンバスからのトポロジー抽出や、Constraint ManagerでのトポロジーによるElectrical Constraint 設定に対応しました。

SystemPI

PI解析向けの新しいWorkflowです。

PKG、PCBといったシステムを構成する各要素の電源モデルを接続し、周波数領域解析、過渡解析といったシステム全体のPI解析を実施できます。- Die Model Editor

- ターゲットインピーダンスの導出

- PDN周波数領域解析

- 電源リップル過渡解析

- IRドロップ解析

ご紹介いたしました機能以外にも設計工程、設計後工程を助け、効率化を行うことのできる多くの機能が含まれております。是非ご活用いただき設計業務の改善に役立ててみては如何でしょうか。

イノテック株式会社

ICソリューション本部 第二技術部 SPBグループ

平井 智

Latest Issue

- Dynamic Duo 2.0と新製品Palladium Z2 およびProtium X2のご紹介

- 医療現場で期待されるハンズフリーソリューション

- ケイデンス・オンライントレーニングの無料アクセスのご案内

- 日本語ブログのご紹介

- Cadence Topics

- SOCのオンチップバス及びメモリサブシステムの性能検証を効率化するSystem VIP

- NUMECAの買収、NUMECA製品の紹介

- 拡張モバイルブロードバンド(eMBB)向けの新しい5G NR設計

- EMX Planar 3D Solver version 6.0アップデートとVirtuoso RF Solution環境から実行できる電磁界解析フロー

- SIGRITY/SYSANLS 2021.1の最新アップデート情報のご紹介

- SDC検証の包括ソリューションツールConformal Litmus誕生 〜 タイミング制約検証の新しい提案 〜

- More Than Mooreデバイスに不可欠なチップレット間通信を実現するケイデンスのIPソリューション

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues