SOCのオンチップバス及びメモリサブシステムの性能検証を効率化するSystem VIP

はじめに

昨今のSOC開発では、機能の複雑化及び高性能化が進むに伴い、扱うデータ量も飛躍的に増えています。

画像処理の例を挙げると、Full HD → 4K → 8K という解像度の増加により、扱うデータの量も4倍、16倍と増えることになります。Ethernetでは100G/400GbpsがIEEEで規格化され、800Gbpsもその検討が進んでおり、PCIeではGen1の5GT/sからGen5では64GT/s(リンク幅x1、双方向)と最大転送帯域は増え続けています。このように、SOCで処理すべきデータの量は今後ますます増え続けていくことが予測されます。

これらの増え続けるデータを処理するために、要求帯域を満たすメモリを接続可能なSOCを設計することになりますが、要求される性能を満たすために、オンチップバスのトポロジやメモリサブシステムをどのように構成するかが重要かつ非常に難しい課題になります。

本稿では、SOCに要求されるオンチップバス及びメモリサブシステムの性能を設計/検証する手法を提案いたします。

SOCの性能を早期に確認する際の課題

SOC開発の現場において、オンチップバス及びメモリサブシステムの性能の設計/検証に責任を負う立場の組織及びメンバーは、以下のような難しい要求に応える必要があります。

- レイアウト工程での手戻りを避けるため、設計の初期段階でバス及びメモリ構成を決定すること

- 製品の要求性能を満たす最適なバス及びメモリ構成にすること

しかし、設計初期段階では以下のような状況であることが多く、性能検証を実施する十分な条件が揃っていません。

- 構成を決定すべき時期にモジュールの設計及び検証が完了していない

- 設計初期段階で性能検証目的のテストベンチを作成する工数が確保できない

上記のような難しい状況の中で、性能を担保する立場の開発者/組織は、過去製品のデータやこれまでの知見を用いた机上での性能見積もりをすることになります。定量的なデータが少ないため、より安全性の高い構成を選択しがちで結果的にオーバースペックなSOCとなってしまうことも少なくありません。

このようなジレンマを解消し、要求に対して最適なオンチップバス及びメモリサブシステムの構成を決定するには、以下のような技術的な課題をクリアする必要があります。

- 課題1:複雑なテストベンチを構築する(ベンチ構築)

- 課題2:製品ユースケースと同等のアクセスパタンを準備する(シナリオ作成)

- 課題3:要求性能を満たすかを確認しボトルネックを特定する(性能解析)

課題解決の手法提案

Cadenceではこれら課題解決を強力にサポートするCadence® System-Level Verification IP (以下System VIP) と呼ばれるツール群を準備しています。

https://www.cadence.com/ja_JP/home/tools/system-design-and-verification/system-vip.html

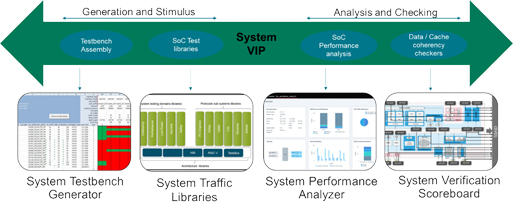

図1 System VIPのツール群

図1に示すようにSystem VIPは以下4つのツールから構成されており、各ツールは単独でも使用することが可能です。

- System Testbench Generator

- System Traffic Libraries

- System Performance Analyzer

- System Verification Scoreboard

ここからは先ほど挙げた3つの技術課題をSystem VIPの利用により解決する手段をご紹介します。

課題1:複雑なテストベンチを構築する

SOCの機能の複雑化に伴い、オンチップバスに接続されるモジュールの数も増えており、200以上のモジュールが接続されるケースもあります。このように大量のモジュールが接続されるオンチップバスの機能/性能検証を実施するためには、以下の条件を満たすテストベンチを構築する必要があります。

- テストシナリオの変更が容易

- テストベンチの構成変更が容易

前述の通り、オンチップバスやメモリサブシステムを検証するフェーズでは、まだオンチップバスに接続されるモジュールの設計が完了していないことがあります。そのようなモジュールの代わりにVIP (Verification IP) やAVIP (Accelerated VIP) を使用します。また、たとえ設計が完了していても、外界と接続される標準インタフェースモジュールは、シナリオの作成が難しいことが多く、VIPやAVIPを使用して容易にテストシナリオを実行可能にする必要があります。このようにVIPやAVIPを使用することで、テストシナリオ及びテストベンチ構成の変更は容易になります。しかし、大量のVIPやAVIPを管理してテストベンチを構築することは非常に手間のかかる作業です。

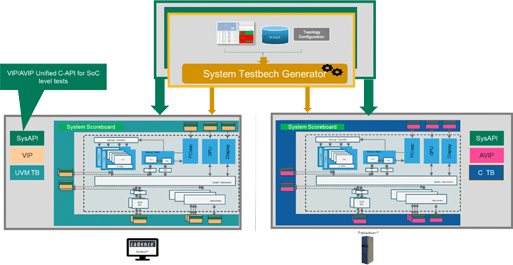

System VIPに含まれるSystem Testbench Generatorでは、テストベンチにインスタンスするVIPやAVIP情報の管理をIP-XACTやCSVファイルで一元化し、それらを入力として自動的にテストベンチを構築することが可能です。それにより、VIPやAVIPのパラメータ変更やインスタンス有無の切り替えが容易になり、テストベンチ構築の効率を飛躍的に向上させることができます。

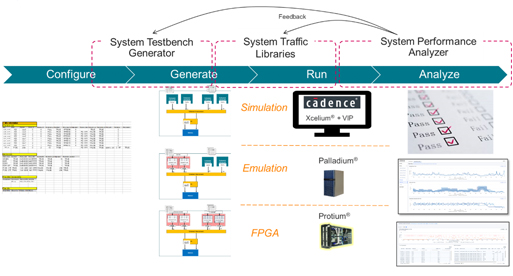

また、図2に示すように、Xcelium™ Logic Simulationで実行可能なシミュレーション用ベンチとPalladium® Emulation Platform / Protium™ Prototyping Platformで実行可能なエミュレーション用ベンチを同一の入力から生成可能です。テストベンチ作成者は、両方のベンチを作成する手間を省くことができ、検証者は検証フェーズ毎にテストベンチを切り替えることが可能となります。

図2 System Testbench Generatorの概要図課題2:製品ユースケースと同等のアクセスパタンを準備する

モデル (VIP / AVIP) を使用した検証で必ず課題になるのは、製品ユースケースと同等のテストシナリオを準備することです。テストシナリオにより製品ユースケースの再現度を高めることが、性能検証の品質を左右します。

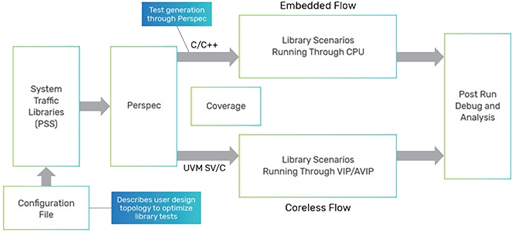

System VIPのSystem Traffic Librariesでは業界標準のインタフェースに対応した様々トラフィック定義をPSS (Potable Stimulus Standard)にて提供しており、製品ユースケースと同等のアクセスパタンを各インタフェースから発生させることを可能にします。特定のVIPやAVIP単独のシナリオが作成できるだけでなく、VIPやAVIP間で依存関係を持ったシナリオや周期的な処理(転送)もシナリオとして作成することができます。

図3に示すように、弊社のPerspecをご使用いただくことで、System Traffic Librariesを利用して、必要な検証環境に応じたテストシナリオを作成することが可能です。

図3 System Traffic Librariesを使用したシナリオ作成のフロー課題3:要求性能を満たすかを確認しボトルネックを特定する

質の高いテストシナリオを実行することが出来ても、性能のボトルネックを特定できなければ質の高い性能検証にはなりません。DUTが大規模になりシナリオが複雑になると、経験のある熟練した技術者が時間をかけてもボトルネックを特定するのは難しい作業になります。

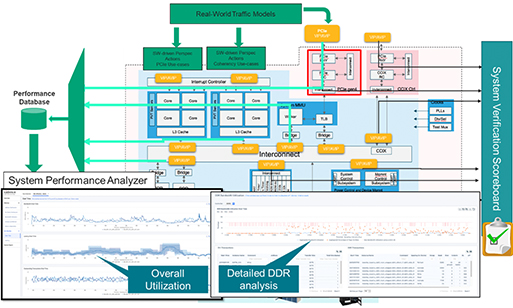

System VIPのSystem Performance Analyzerはテストベンチ上で抽出したトランザクション情報を収集し、オンチップバス及びメモリサブシステムの性能に関わる情報をGUI上に可視化することができます(図4)。

図4 System Performance Analyzerの概要図性能に関わる情報を可視化することで、性能のボトルネック特定作業の効率を飛躍的に向上させることができます。また、VIPやAVIPから実際のRTLへ置き換えて製品ユースケースのシナリオを実行した際でもSystem Performance Analyzerを使用することができるため、設計初期段階で見積もった性能とのコリレーションを取ることも容易になります。

System Performance Analyzerもこれまで説明してきたツール同様にシミュレーションでもエミュレーションでも使用することが可能です。

機能検証でのSystem VIPの活用

ここまでは性能検証に着目してきましたが、System VIPは機能検証でも活用することができます。

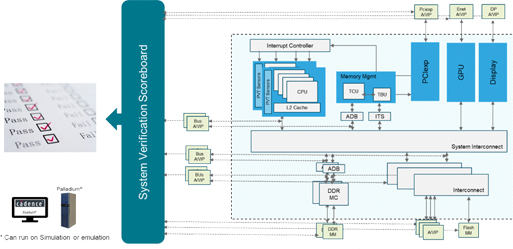

図5はSystem VIPのもう一つのツールであるSystem Verification Scoreboardの概要を示したものです。 System Verification ScoreboardはSOC内で様々に変化するトランザクションのデータ完全性を自動的にチェックする機能を有します。また、コヒーレントなインターコネクトやメモリのインタフェースをサポートするため、バストランザクションとメモリのRead/Writeコマンドとのコリレーションを取ることも可能です。さらに、ユーザ固有の機能を検証するために拡張することもでき、システムレベルのデータフロー及び整合性の検証効率を大幅に向上させることが可能です。

図5 System Verification Scoreboardの概要図

テストベンチ構築ではSystem Testbench Generatorを活用し、テストシナリオ作成でSystem Traffic Librariesを活用することで、性能検証と機能検証でテストベンチとテストシナリオの共通利用が可能となり、ベンチ構築やテストシナリオ作成の工数を削減することができます。

まとめ

CadenceのSystem VIPを利用して、SOCのオンチップバスやメモリサブシステムの性能検証の効率を上げるだけでなく、検証の品質を向上させる手段を紹介してきました。図6は、これまで述べてきたSystem VIPに含まれる3つのツールが、性能検証のどのフェーズで利用可能かを示しています。それぞれのツールで各フェーズでの作業効率を飛躍的に向上させることができます。

図6 性能検証でのSystem VIP適用フェーズ

System VIPの詳細につきましては、以下のページをご覧ください。概要説明のビデオやユーザ事例の紹介もございます。

https://www.cadence.com/ja_JP/home/tools/system-design-and-verification/system-vip.html

ご興味のある方は弊社営業までお問い合わせください。

フィールドエンジニアリング&サービス本部

システム&ベリフィケーション

Latest Issue

- Dynamic Duo 2.0と新製品Palladium Z2 およびProtium X2のご紹介

- 医療現場で期待されるハンズフリーソリューション

- ケイデンス・オンライントレーニングの無料アクセスのご案内

- 日本語ブログのご紹介

- Cadence Topics

- NUMECAの買収、NUMECA製品の紹介

- 拡張モバイルブロードバンド(eMBB)向けの新しい5G NR設計

- EMX Planar 3D Solver version 6.0アップデートとVirtuoso RF Solution環境から実行できる電磁界解析フロー

- SIGRITY/SYSANLS 2021.1の最新アップデート情報のご紹介

- プリント基板設計ツールAllegro/OrCAD:SPB17.4-2019 QIR2 最新機能改善と便利機能のご紹介

- SDC検証の包括ソリューションツールConformal Litmus誕生 〜 タイミング制約検証の新しい提案 〜

- More Than Mooreデバイスに不可欠なチップレット間通信を実現するケイデンスのIPソリューション

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues