チップ-パッケージ-PCB設計環境の統合化によるRF製品設計フローの最適化

現在の設計フローは、EDAツール間の連携が不十分なため、様々な設計作業を分断せざるを得ない状況にあります。分断化したフローを使用していると、システムや回路が複雑化し、帯域の余裕がなくなったり、デバイスサイズの小型化や実装形態の多様化に対応できないなど、新たな問題を解決することが難しくなってきます。今回は、Cadence® Virtuoso® RF Solutionを通じて、設計チーム間の連携性を高めるとともに、次世代のハイエンドなRF製品設計に生かすことができる、垂直統合型のフローをご紹介します。

はじめに

回路シミュレータが導入された当初から、設計フローはなかなか統合されない状況が続いてきました。さらに、電磁界解析などの特殊な用途のツールの出現のより、フローはより細分化されてきました。回路シミュレーション、レイアウト、電磁界解析は、それぞれ別々のツールを別々の担当者が使用しているのが一般的です。以前は、設計が比較的シンプルで、共通のインターフェースポイントをサブシステムで定義することができていたため、別々のツールでも対応できていました。また、これらの設計では、アルミナやグラスファイバー等の高周波向け基板上にシングルチップのパッケージを実装する方法を採用していました。これも、チップ、パッケージ、PCBの設計が完全分業していた要因です。このような従来型の設計に代わり、最近では、マイクロバンプ、スタックチップ、シリコン・インターポーザ、FOWLP、部品内蔵基板など、より複雑かつ高度な実装が主流になってきています。

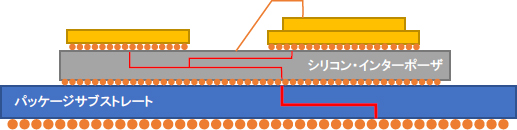

ここで、図1のようなスタックチップの設計を考えてみましょう。この設計では、1つのサブシステムとして機能することを想定しています。高周波設計の観点から、ある領域の電磁結合は、スタックしている他の領域に影響を及ぼすことは明確です。しかし、複数の設計チームが異なるEDAツールを使用して設計していたとすると、これらの干渉を考慮した設計を行うことは難しくなります。分断化されたフローにおいては以下のような問題に対処することができません。

- システムや回路の複雑さの増大

- より厳しい動作帯域

- 動作電力のさらなる低減要求

- デバイス・製品サイズの小型化

- 進化し続けるパッケージ技術・製造技術からの要求

- デバイス・実装コスト低減要求

図1:スタックチップ設計

分断した設計フローの課題

半導体デバイスのプロセスは数百nmから数nmに一気に縮小されました。より小さなテクノロジ・ノードで製造されたLSIはあらゆる面で製品を改善しますが、これらのダイを実装するパッケージやモジュールにおいても、より小さくしなければ意味がありません。より小型のパッケージに集積度を高めてデバイスを詰め込んだ場合、デバイス間の干渉は増大しますので、電磁界解析を併用したレイアウトの最適化が必須になってきます。

ほとんどの設計ではCMOSが採用されていますが、高周波帯域においては、一部SiGe, GaAs, GaN, InPといった化合物系のプロセスとのマルチテクノロジ設計や、SAWやBAWなどのフィルタテクノロジが必要となります。ひと昔前、Gordon Mooreは、パフォーマンスと費用対効果の向上のためにマルチテクノロジの採用を提唱しました。

「大規模システムの構築にあたり、小機能の個別パッケージを接続する方が経済的であるかもしれない。機能設計と構造を組み合わせた多機能化により、大規模システムベンダーはかなり多様な機器を迅速かつ経済的に設計及び構成できるようになるはずである。」[1]

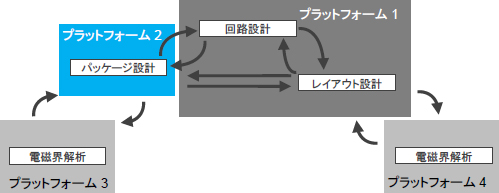

このように、非常に複雑な設計のあらゆる箇所が相互干渉するため、検証には通常以上の時間を要します。それにもかかわらず、アグレッシブなスケジュールの中で、新しくかつ難しい設計課題に取り組むことが求められます。そのスケジュールを守りつつパフォーマンスを向上させるには、同時並行設計を意識することが重要となります。設計に割く時間が不足することで、回路と電磁界シミュレーションに十分な時間を割くことができなくなり、LVS検証も不十分になる可能性があります。このため、電気的なパフォーマンス検証に不可欠な電磁界シミュレーションを行わずにテープアウトせざるを得ないこともあります。さらに設計チームが複数の異なる設計プラットフォームを使用している場合、より複雑な問題が発生する可能性があります。例えば、解析担当者が行った変更が製造担当者のプラットフォームに反映されないといった場合や、予期しないLVSエラーの発生、さらには、検証過程で意図せずに過去の電磁界解析の結果を使用していたといったものがあげられ、設計フローにおける混乱の要因になります。共通のプラットフォームを採用していないことにより、ツール間での情報のやり取りにおいてもエラーが発生しやすくなります。ツール間でレイアウト情報をやり取りし、電気的パフォーマンス検証のためにシミュレーション環境に引き渡します。この際、設計変更のトレーサビリティが欠如しているため、変更の反映が遅れたり、失われたりして、製造の際に問題が生じる場合があります。問題のタイプに応じて複数の電磁界解析ツールや解析技術を使用している場合、問題点を見落としたり、時に不良が生じたりする可能性も考えられます。

この分断化した設計アプローチでも最終的には動作するデバイスの設計を行える可能性はありますが、一体となった設計フローではないため、問題個所の特定やエラーの対処に時間がかかる可能性があります。このため、より検証に必要な時間が短縮できるよう、最小限の設計変更で済ませるため、過去に検証済みの設計データに頼る傾向になりがちです。このフローに潜在するこの見えないコストは、市場における製品の差別化に必要な、革新的技術開発を妨げる要因となります。技術革新の欠如は、過去25年間で多くのマーケットリーダーによって非常に有害であることが証明されています。

図2:複数のEDAツール間のデータ交換

何が必要なのか...

次世代の高周波製品を生み出すためには、設計チーム間でコラボレーションが不可欠となります。コラボレーションをスムースに行うためには、統合された設計フローが必要です。一方で、設計者が日々使用している設計環境を大幅に変更すると、設計効率が著しく低下します。このため、設計者がすでに利用しているプラットフォームで実現すべきと考えます。日々スケジュールに追われる設計者が新しいプラットフォームを採用する際、その手間と習得にかかる時間は計り知れません。Cadence Virtuosoアナログ設計環境は、Cadence Spectre®回路シミュレーションプラットフォームおよびSpectre RFオプションとともにエレクトロニクス設計業界で最も広く使用されているプラットフォームです。ほとんどのエレクトロニクス設計者は、VirtuosoのカスタムIC設計プラットフォームのユーザであるか、このプラットフォームのトレーニングを受けています。このプラットフォームは他のどのEDAツールよりも多くのファウンダリーにサポートされています。また、多くの組織内のCAD担当者がVirtuosoプラットフォームをサポート可能です。一方、パッケージングテクノロジが複雑になるため、様々な実装形態に対応したパッケージ設計ツールが必要となります。Cadence SiP LayoutとCadence Allegro® PCB 設計プラットフォームは、多種多様な実装形態に対応した、業界で多数の実績を持つパッケージ/PCB設計ツールです。また、VirtuosoカスタムIC設計プラットフォームは、高度なマルチテクノロジ、スケマティック・ドリブン・レイアウト、階層設計機能も備えています。

Virtuoso RF設計フロー

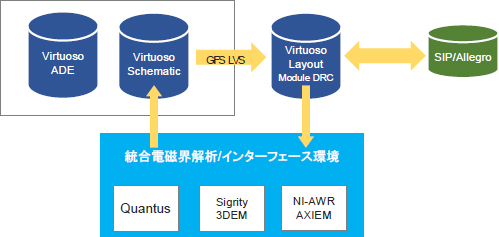

Virtuoso RF設計フローは、これらのプラットフォームの総合力をフル活用しており、モジュール、パッケージ並びにPCB設計を単一の環境で設計するために必要な回路シミュレーション、レイアウト、電磁界解析、検証機能を備えた、スケマティック・ドリブン・レイアウト環境を提供します。

図3:Virtuoso RF設計フロー

Virtuoso RF設計フローの主な利点をいくつか見てみましょう。

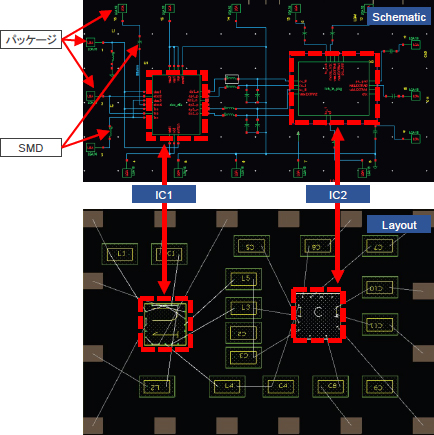

シングル・ゴールデン・スケマティック

Virtuoso RF設計フローでは、回路シミュレーション、LVS、電磁界解析、検証に対して、マスターとなるゴールデン・スケマティックを供給します。このため、電磁界解析やLVSを行うために特別な回路図を用意する必要がありません。これは、従来のICの回路図とは異なり、ICだけではなく、モジュール全体もしくはパッケージ全体の接続情報も含まれています。

図4:Virtuoso Schematicによるパッケージ接続

マルチテクノロジーサポート

Virtuoso RF設計フローは、Virtuosoプラットフォーム内のマルチテクノロジサポート(MTS)を活用しています。Virtuoso回路図とパッケージレイアウト間をリンクし、パッケージのパッドやSMD、IC間の接続をフライトライン(ラッツネスト)として表示します。この例では、各チップは個別のテクノロジであり、もちろんパッケージとSMDも別のテクノロジを持っています。

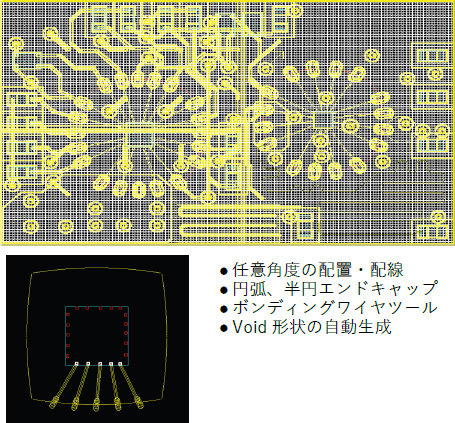

配線機能の拡充

Virtuoso RFソリューションは、有機基板パッケージの配線スタイルに対応し、ボンディングワイヤや、任意角度の配線・部品配置をVirtuosoの環境内で実現しました。このUIでは、円弧や円も多角形で近似されることなく、厳密に表現されます。さらに、電源・グランドプレーンのダイナミックカッパー(Void形状の自動生成)もサポートしています。自動ボンディングワイヤ配置用ガイド生成を含む、新しい配線機能を図5に示します。複数ボンディングワイヤを1回の配線プロセスで配線することも可能です。

マルチチップ・モジュール(MCM)設計においては、ダイのテープアウトとほぼ同時に、実装部品、モジュール内の配線を決定できるところまで追い込むことができます。

図5:Virtuoso RFにおけるパッケージ配線機能

VirtuosoとAllegroのシームレスなインテグレーション

Virtuoso RFフローには、SiP Layout/Allegroプラットフォームからパッケージとモジュールの設計データをインポートすることができます。さらには、これらの設計データを編集したり新規に設計をしたりすることも可能です。逆に、VirtuosoのレイアウトをSiP Layoutに持って行き、SiP Layout上で編集したり、製造性チェックを行ってからインポートすることもできます。これにより、クリティカルパスと構造をいち早く検討でき、電気的な影響があるレイアウトの部分を簡単に評価できるようになります。

寄生抽出と電磁界解析

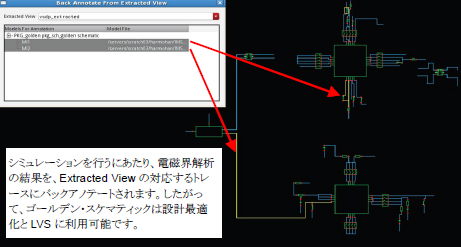

設計が進み、レイアウトの生成段階になると、配線カップリング、インピーダンス不整合、挿入損失、伝送線路の分布等、レイアウトによって引き起こされる電気的影響を検証します。これには、寄生パラメータ抽出と電磁界解析ツールを使用します。Virtuoso RFソリューションには、電磁界解析環境が組み込まれており、設計データ全体もしくは特定のトレースやインスタンスを対象とした解析を行うことができます。電磁界解析の設定は、Virtuoso Layoutの環境内で行え、結果のSパラメータや集中定数等価回路モデルは、ゴールデン・スケマティックのExtractedセルビューに自動的に取り込まれます。寄生パラメータのような電磁界解析の結果をExtracted Viewで表現することで以下のようなメリットがあります。

図6:電磁界解析の結果をゴールデン・スケマティックにバックアノテーション

- 回路図内にSパラメータブロックがインスタンス化されているような別の回路図シンボルが不要となります。

- ゴールデン・スケマティックには、回路設計情報を壊すことなく電磁界解析の結果を取り込むことができ、レイアウトによる問題を含むシミュレーションやLVSに利用可能です。

- Hierarchy Editorでは、ビューを組み合わせたり、比較することで、簡単かつ迅速に回路設計への影響を検証することが可能です。この機能を図6に示します。ここで、回路図中の2つの黄色い配線には、「Back Annotate from Extracted View」ウインドウで選択した、M1とM2の電磁界解析の結果が割り当てられていることを示しています。

Virtuoso RF設計フローは、電磁界解析エンジンとして、Cadence Sigrity™ PowerSI® 3D EM Extraction(フル3次元アダプティブ有限要素法解析エンジン)とNI-AWR AXIEM(モーメント法エンジン)の2つを採用しています。

IC, パッケージ, PCBの統合フロー

Virtuoso RF設計フローでは、チップとパッケージ、PCBのレイアウトを1つのキャンバス上に表示し、混在するテクノロジのアライメントや統合編集が可能になります。チップとパッケージの統合編集のイメージを図7に示します。

チップはVirtuosoのカスタムIC設計プラットフォームで設計し、ここでは、パッケージ情報はSiP Layoutで作成したものをインポートしています。ウインドウ上部のタブでは、それぞれ単体の設計を切り替えることができ、連携した編集作業が可能となります。シミュレーション用の電磁界解析の結果は、それぞれのトレースにバックアノテーションされ、Extracted Viewに含まれる形になります。したがって、ゴールデン・スケマティックは、設計最適化とLVSの両方に利用可能となります。

チップ階層が表示されている場合、テクノロジ・レイヤの選択とSIP_BGAレイヤの選択が可能で、かつ編集することができます。VirtuosoカスタムIC設計プラットフォームではチップとパッケージ両方の回路図定義を行い、当然、チップとパッケージの間のインターフェースの定義も行います。コネクティビティを保持するため、パッドやボールの位置を編集すると一体となって移動します。パッケージとチップのアラインメントが崩れた場合、回路図の接続情報からフライトライン(ラッツネスト)を表示して、未結線であることを示します。

これにより、ICとパッケージの設計チームは独立して作業をすることができることに加え、チップレイアウトとパッケージレイアウトのフットプリントのずれを即座に吸収することができます。一方で、統合編集モードを使用することで、チップとパッケージの同時編集も可能となり、常に両者を同期させた設計も可能となります。

図7:チップ-パッケージ統合設計モード

まとめ

Virtuoso RF設計フローは、 次世代の高周波製品設計に必要な、シミュレーション、レイアウト、寄生抽出、電磁界解析、LVS、DRCをシングルフローにまとめた統合環境を提供します。このフローにより、設計担当分野を超越したコラボレーションを実現し、従来の設計データを流用したレイアウト検証に時間を割かずとも、より革新的な設計に時間を注ぐことができます。寄生抽出と電磁界解析ツールのシームレスな統合により、生産性は向上し、分断化されたフローによって発生する各種エラーを削減することが可能になります。

結論として、Virtuoso RF設計フローは、次世代の高周波製品を設計するために最適な環境と言えます。

References

[1] G. Moore, “Cramming More Components onto Integrated Circuits,” Electronics, vol. 38, no. 8, p. 114, 1965.

※本資料はWhite paper: Consolidating RF Flow for High-Frequency Product Design(Michael Thompson, Senior Solutions Architect, Cadence)を和訳したものです。

日本語訳:

カスタムIC&シミュレーション

アプリケーション・エンジニア

人見 忠明

この記事に関する問い合せ先:

コーポレート・マーケティング部

E-mail:cdsj_info@cadence.com

Latest Issue

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues