【寄稿記事】

レイアウト効率向上に関する検討事例とケイデンスへの期待

執筆者プロフィール: 諏佐 聡子氏 東芝マイクロエレクトロニクス株式会社 |

|

EDA部門でPDK開発やB/Eツールのサポート、導入評価を担当した後、数年前に現在の設計部門に異動し、主にレイアウト設計を行うと共に現場での設計効率改善に取り組んでいます。EDAと設計での双方の経験をふまえ、この場をお借りしてお話したいと思います。

1. アドバンスドノードプロセス

1.1 Virtuoso® ICADVの利用

アドバンスドノードの設計は、Virtuoso ICADVの利用によって非常に助けられています。

当初は、従来のVirtuosoでの設計も検討しましたが、デザインルールや制約への対応は相当困難でしたので、結局はアドバンスドノード向けのVirtuoso ICADVを利用することになりました。

これまでには無かったデザインルールの理解をしながら、そのルールに適応した機能を使いこなすことは大変でしたし、慣れるまでは時間がかかりましたが、プロジェクト開始前からトレーニングの実施やオンサイトでのサポートなど、ケイデンスから全面的にご協力をいただきましたことで、プロジェクト着手時の苦労がだいぶ軽減されたと思っています。ありがとうございました。

通常、レイアウトのツールを導入する際、適用するデザインルール・制約条件・ゴールとするレイアウトを実現できるよう格闘しますが、アドバンスドノードの場合はルールが複雑すぎて、逆にツールの動作によってレイアウトの制約やルールを知るような局面も多々ありました。今後世代が進むにつれ益々ルールが複雑化し、ツールに任せる割合が増える傾向にあると聞いていますので、今後も引き続きアップデートに期待しています。

1.2 社内Fabと社外Fabの利用環境の違い

アドバンスドノードの設計に移行していくことで、そのPDKを開発した担当者が身近にいないことや、社内のPDK開発者が少なくなることは、間接的に今後の課題となっていくかもしれません。

PDK開発者が身近に居れば、そのPDKを利用する設計者との間で直接の交流が持てるので色々な情報交換が出来ますし、設計者から直接質問したり、社内特有の設計手法に合わせた機能を要望したりすることが可能です。

また、PDK開発者が開発中にケイデンスの担当AEにヘルプをいただく中で、ツールの使い方・新機能・注意点、PDKの設定とツールの動作の関連性などの知見が蓄積されていき、それを設計者に展開していくことができます。

PDK側でいろいろなファンクションがインテグレートされていても、その情報が設計者に伝わらなければ、非常にもったいない事になってしまいますし、社外のFabにシフトしていく中で社内のPDK開発者が減れば、気軽にアクセスできる「詳しい人」が減っていくかもしれません。

設計者として日々の業務に追われていると、セミナーやトレーニングに参加して常に新しい情報に接することはなかなか容易なことではありませんが、これまでとは別の方法で、ケイデンスから新情報や提案を受けるような仕組みを作っていきたいと考えています。

2. ツールの進化と設計への適用

2.1 EDAと設計の視点の違い

以前EDA部門に所属していた時は、ツールの新機能、自動配線の実行速度や配線率、寄生抽出の精度やツールごとのパフォーマンス比較などに注目しがちでした。しかし、設計部門に異動し自ら設計に携わるようになってからは、考えが変わってきました。

たとえば、自動配線の実行速度が短縮されても、セットアップや条件設定ファイルに時間がかかり、操作方法が分かりにくければ、トータルとしてTATは長くなり、使用者には最終的にストレスが残ります。

それでも、最後までやり通す事ができれば次回の設計でも使ってみようと思えますが、うまくいかずに旧来の方法に戻ってやり直すような最悪の結果で終った場合は、もう恨みしか残りません。

EDA部門にいたころは、まずツールのトレーニングを受け、ケイデンスからマンツーマンの手厚いサポートを頂きながら、特定のツールを毎日使って操作に習熟した状態で、既に作りこんだ条件設定を使ってツールの評価を行っていました。

この前提で、ツールの操作性や、実行時間と結果のデータを観測して評価結果を出していたのに対して、現場の設計者にとってそのツールに関わるのは長い設計期間の中のほんの一部であることが多いです。

制約や回路特性に注意が必要な設計の場合、1人の設計者がF/EからB/Eまでを担当する場合もあり、どうしても個々のツールに触れる期間は短くなりがちです。1つのプロジェクトに半年かかるとするなら、各ツールの使い方を覚えても次回それを使うのは半年以上先のことになります。

仮に実行時間が半減するとしても、次にいつ使うか分からないツールのトレーニングを受けたりマニュアルを読んだり、セットアップを間違えて実行をやり直したりしているよりも、旧来の手法でやったほうが確実に早いということも、新しいツールの使用を躊躇する大きな原因になっていると考えています。

2.2 具体例

この場ではアドバンスドノードプロセスの話は避けまして、従来のプロセスにおける取り組みと、そのときの困難について、ご紹介します。 私の所属する設計課では、主にI/Oの設計を回路からレイアウト、ライブラリまで一貫して開発しています。

I/Oの場合、通常動作時の動作電流だけではなく、内部回路がESD(静電気放電)で破壊されないような対策として、ブレイクダウン電圧を考慮したPower Clamp配置やそれに接続する配線の電流密度や配線抵抗など、考慮すべき点が多岐にわたります。

近年プロセスの微細化が進むにつれ、配線幅の絶対値が小さくなり、流せる電流量が減る傾向にあるため、相対的に単位面積当たりの配線幅が大きくなり、配線後のセルサイズの見積もりが難しくなっています。

加えて、素子も小さくなったため、MOSのL/W以外のパラメータ値も変えないと、太い幅の配線が、複数のレイヤでスタックした場合に、これらを接続することができなくなってきました。

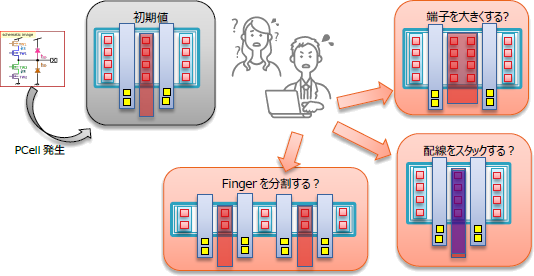

しかしながらVirtuosoが想定するフローは、最初に回路定数(素子サイズ)を決定して、そのサイズで生成したレイアウト素子(Pcell)を使って配置配線する事が前提になっています。

一般的な回路でも配置の制約や、全体の収まりの都合で、キャパシタのアスペクト比を変えたり、MOSのFingerを分割したりして、素子のパラメータを調整することはありますが、それに加えてI/Oでは、更に配線幅を稼ぐためにMOSのゲートピッチを広げたり、Finger数とMultiplier数を変更したりして、最大電流量に適応した幅での配線が可能な素子形状を作成します。その後、その素子が目標とするサイズ内に収まるかというレイアウト上の検討を何度も繰り返しています。

このようなときに、規定した一意の値のPcellを生成するのではなく、セルサイズに収まる範囲で何種類か候補を提示してくれるとか、またはフロアプランナーが最適形状を選択・提案してくれれば、設計効率の改善が期待できるのではないかと考えています。

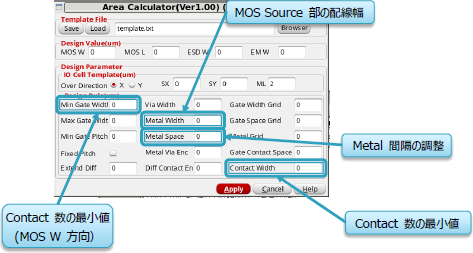

この課題に対して、現在弊社では独自の取り組みを行っております。(この詳細はCDNLive 2017で紹介しました。)

従来は、配置可能領域を計測し、MOSのL/W/Fingerの値を割り振りながら最適値を求めていましたが、一部の値を指定することにより、その他の値を計算するユーティリティを開発し、設計者の頭の中で行っていた作業を自動化しています。

独自に開発したこのユーティリティを活用する事で、やり直しや計算ミスが少なくなりました。また、条件を満たす素子形状を生成するのにかかる時間は、従来比で平均約70%時間短縮できる等、大きな効果が得られています。

また、最近ではEAD (Electrically Aware Design)によるEM検証が可能になりました。

I/Oの場合、EMだけではなくESDの考慮も同時に行う必要がありますが、現時点ではESDをIn-Designで検証するのは難しく、従来どおり設計後に別のツールでESD検証を行っています。

設計後にESD検証でエラーが見つかると、通常その修正は大がかりになってしまうことが多いため、これらの修正作業の短縮を可能にする新機能の登場に期待しています。

次に紹介したいのは、バス配線に関する最近の事例です。

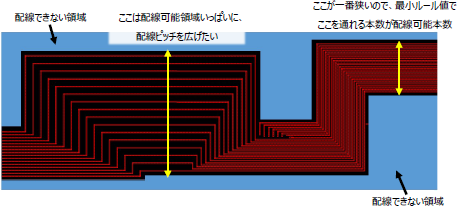

配線幅の10万倍以上の配線長で、100本以上の束を配線する際に、自動配線ではなくCreate Busコマンドを使用しました。 配線領域として使える領域が限られおり、たくさんのレイヤを使用して立体的なバスにしなければならなかった事、またその配線領域の幅が一定ではなく途中で何度も変わっていたために、バスの途中で一部のネットだけレイヤを乗り換えたり、ピッチを変更したりする必要があったり、と状況はかなり複雑でした。

また一旦配線が終りましても、配線後のレイアウトを寄生抽出してシミュレーションしたところ、一部のネットの寄生容量が大きすぎて回路動作に影響があることがわかりました。 そこでまず水平方向(同一レイヤ間)の寄生容量対策として、途中でバスのバンドルから離脱して数が減るに従って、ピッチを順次広げるため、線分単位を対象にDRD Compactorを使ってピッチを変えました。 次に上下方向(異レイヤ間)の寄生容量対策として、上下の配線をぴったり重ねるか、互い違いにするか、それとも半分重ねるか、など色々なパターンで配線しなおして検討を繰り返し、最終的には手作業での処理になりました。

それ以前にCreate Busコマンドで100本以上を同時に扱うのはパフォーマンス的に難しかったことから、何回にも分けて配線しなければならず、配線後にはシミュレーションの結果を確認しつつ何度も編集作業を行う必要がありました。 そこで独自のノウハウを盛り込んだSkillプロシージャーを作成することで、シミュレーションの結果を反映したバスの編集作業が大きく効率化できるようになり、場所によっては既存手法で1日かかる作業が、1時間も掛からずに完了するような効果を挙げることができました。

今回の事例は、カスタムレイアウトのバス配線としてはかなり大掛かりなものでしたが、配線幅とピッチの指定だけではなく、例えばバス配線の配線領域の幅・バスの本数・バスのピッチの値のどれかを指定することで、自動的に残りの値が決まるような機能があれば、もっと効率よく配線できたのではないかと考えています。

既存のバス配線に対する編集機能の今後の充実に期待しています。

2.3 ケイデンスへの要望

個々の局面で使用するツールの種類が増え、各ツールが細分化・高機能化する中で、ツールのパフォーマンスや機能面だけではなく、セットアップの容易性・操作の分かりやすさ・各ツールの統一性などの向上にも是非取り組んでいただきたいです。

トレーニングを受けたりマニュアルを読んだりしなくても、直感的に分かるようであれば一番良いですが、そこまでいかなくても初めて使用するときの高い壁をなるべく低く、そして最後まで安定してゴールできるようなツールの提供をお願いしたいです。

更に設計現場から、「これが昔からあれば良かったのに」と言いたくなるような更新が続きますことを期待しています。

今後ともよろしくお願いします。

Latest Issue

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues