最新CMP平坦化シミュレーション技術と適用事例

膜厚ばらつきとその影響

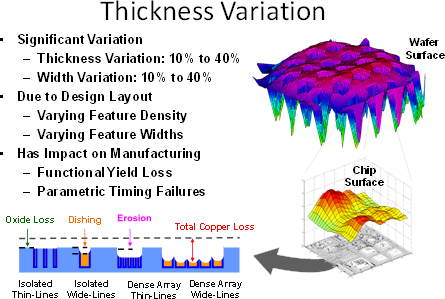

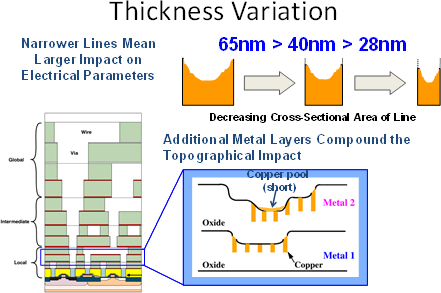

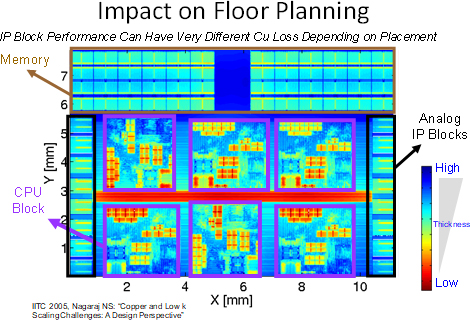

半導体製造ではプロセス微細化や複雑化に伴い、膜厚ばらつきの影響が顕著になってきていて、特にメモリデバイスやイメージ・センサでは、積層での平坦化、貼り合わせでの表面ばらつき制御が難しくなってきています。研磨時間、研磨圧力といったCMP (Chemical Mechanical Polishing) 製造プロセス条件以外に、レイアウトの複雑化が要因としてあげられます。例えば、Cu (銅:配線材料)では、図1に示すように、太幅配線でCuが削れてしまうディッシング現象、細幅配線のアレイで酸化膜が削れてしまうエロージョン現象があり、それら表面高さのばらつきはリソグラフィー工程でのDoF(Depth of Focus:焦点深度)ホットスポットを誘発し、製造歩留り悪化の原因となります。特に28nmプロセスノード以降では、配線幅が細くなるため、膜厚研磨量の断面積に対する割合が高くなり、配線抵抗と配線容量のばらつきが大きくなり回路性能に影響します。また、多層配線の下層の凸凹の影響により、Cuプーリングで配線ショートが問題になる場合があります。(図2 参照)下地層、STI (Shallow Trench Isolation)やPMD (Pre-Metal Dielectric)やW (Tungsten)などのCMPプロセスの影響も大きく、FEOL (Front End of Line)/MOL (Middle of Line)/BEOL (Back End of Line) トータルでの積層膜厚ばらつき考慮が必須となっています。

図1: 膜厚ばらつきの要因とその影響

図2 : 膜厚ばらつきの影響は微細化で顕著

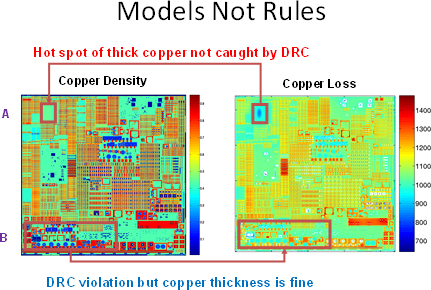

デザインルールのチェックだけでは不十分

膜厚ばらつきを抑えるために、密度、配線幅、配線間隔など最適化し、デザインルールでチェックする方法がとられています。しかし、CMPの影響は広範囲であるため、局所的なデザインルールでのチェックでは不十分であることがわかっています。図3では左側が密度プロット、右側は膜厚プロットを示していますが、密度分布と膜厚分布が対応していない個所が存在し、左上A領域は、密度はデザインルール内ですが、膜厚が極端に薄くなっています。逆に、左下B領域ではデザインルールで違反がでていますが、膜厚ばらつきはみられません。このように、デザインルールだけで、膜厚ばらつきを抑えるのは困難であることがわかります。

図3 : デザインルールと膜厚ばらつきが対応しない事例

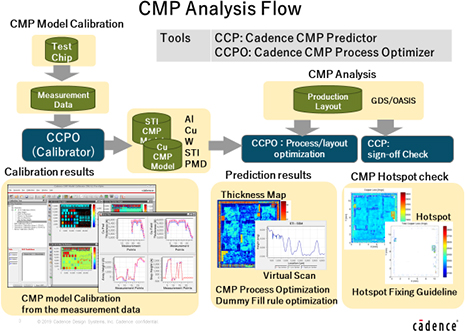

CMP解析フロー

CMPシミュレーションを使用するためにはCMPモデルの準備が必要です。ファウンダリより入手する方法と、自社Fabの場合は実測データよりCadence CMP Process Optimizer™ (CCPO)のCalibrator機能で生成する方法があります。 後者は、アレイのテストパターンが含まれたTEGを用意し、CMPプロセスを振った数種類のウェハを作成し、膜厚データを取得します。そのデータを入力としてキャリブレーションを実行しCMPモデルが生成されます。このモデルは、製造プロセスとレイアウト設計、両サイドからの平坦化アプローチに適用されます(図4 参照)。また、先端のCMPモデリングによる平坦化プロセス最適化では、アプライド マテリアルズと共同開発プログラムで協業しております。

図4 : CMP解析フロー

製造プロセス側からの平坦化アプローチ

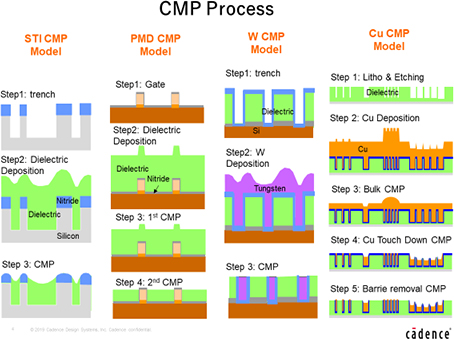

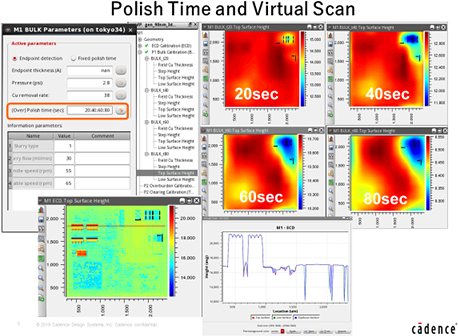

CMPプロセスは複数の工程から成り立っています。Cuプロセスは5つの工程があり、PMD (Pre-Metal Dielectric)プロセスでは4つの工程があります。(図5 参照)それぞれの工程毎にプロセスを最適化することが最終的な平坦性ばらつきを抑えるのに必須となります。CCPOでは工程毎に、研磨時間、研磨圧力といったCMP製造プロセス条件を変更し、チップの膜厚分布をシミュレーションします。図6には、研磨時間が20, 40, 60, 80秒と変化した場合に、膜厚が徐々に削れていく様子が観察できます。指定した断面の膜厚分布をVirtual Scanプロットで表示することで、詳細な膜厚段差を確認することも可能です。このように膜厚はプロセス条件とレイアウトに大きく依存しますので机上での予測が非常に困難です。CCPOを活用することでプロセスエンジニアは、実際ウェハを作成することなく、様々なデザインでシミュレーションすることにより最適なプロセス条件をみつけることが可能になります。また、STI-> PMD->W-> Cu ( M1) -> Cu (M2) -> Cu (M3) -> Cu (M4) -> Cu (M5)といった積層でのシミュレーションにより、下地の膜厚ばらつきの上層への影響をフルチップでシミュレーションします。高精度モデル生成のため、パタンスケールでの形状シミュレーション(feature-scale topography prediction)機能や平坦性改善のためのリバース・エッチバック(advanced reverse etch-back)機能など組み込まれています。

図5: CMPプロセス工程

図6 : 研磨時間毎の膜厚分布とVirtual Scan プロット

レイアウト設計側からの平坦化アプローチ

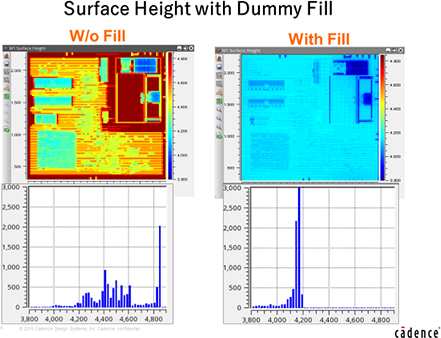

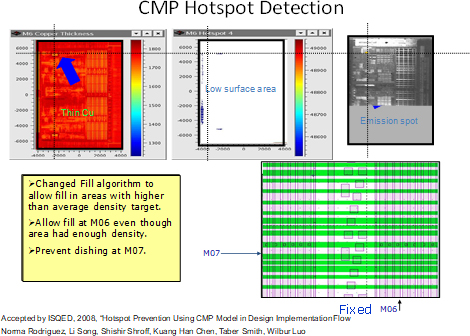

レイアウト設計での平坦化改善手法の一つとして、ダミーフィルがあります。パターンが少ない領域にダミーのパターンを生成し、密度の疎密を少なくすることで平坦化する手法です。ダミーフィルにより配線容量が増加し、タイミングに影響するため、最適なダミーフィルルールで平坦化を実現することが課題となっています。Cadence CMP Predictor™ (CCP)では、どのようなダミー形状をどのくらい生成すれば平坦化が可能になるかシミュレーションし、チェックします。図7はDummy Fillにより表面ばらつき分布が小さくなることを示しています。さまざまなDummy Fillパターンで、平坦化にどう影響するか、回路にどう影響するかをあらかじめ検証することができます。図8は、CCPで実ウェハと同じ個所にホットスポットを検知し、最適なダミーフィルでホットスポットが修正されたことを示した事例になります。このようにCCPは最適なダミーフィルの検証に有効であることがわかります。最近は、微細化に伴う配線の高密度化で、ダミーフィルの最適化だけではホットスポットが修正できないケースもでてきているため、28nmプロセスノード以降では設計段階でのCMP考慮した設計が必要になってきています。図9は同一のブロックを位置や向きを変えて配置したときの膜厚分布で、ブロック内での膜厚が薄い個所と厚い個所の位置が、それぞれのブロックで異なっています。周囲にどのようなパターンがきても平坦化が実現するCMPロバストな設計が期待されます。Black Box Flow機能やVirtual Dummy Fill機能により、ブロック周辺に様々なパターンを仮想的に配置したときの膜厚シミュレーションを行い、ブロックを最適化する手法も用意されています。 また、スクライブラインのパターンの影響も無視できないため、1つのチップだけでなく、スクライブラインを含むフレーム内にアレイ状に並べたショット全体での大規模領域のCMPシミュレーションが必須になっています。CCPでは、大規模領域での実行時間短縮のため、デザインを階層的に処理するStitching Geometry Extraction 機能が組み込まれています。

図7 : Dummy Fillの平坦化への影響

図8: CMP ホットスポット検知と修正

図9 : ブロックの位置と向きによる膜厚分布の差異

膜厚ばらつきを考慮したRC抽出手法

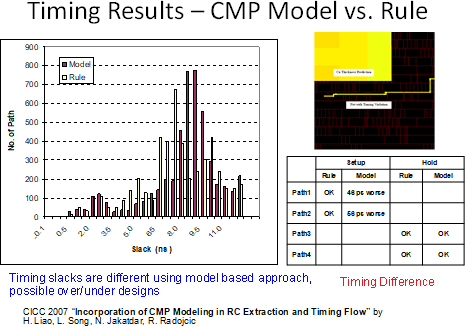

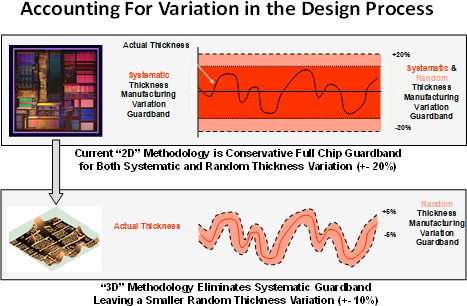

前述した平坦化改善手法を駆使して、膜厚ばらつきを最小におさえることができたとしても、完全にゼロにするのは不可能です。特に28nmプロセスノード以降では、配線幅が細くなるため、、膜厚研磨量の断面積に対する割合が高くなり、配線抵抗と配線容量への影響が顕著になります。膜厚が薄くなれば、配線の断面積減少により抵抗は増加し、容量もばらつきます。膜厚シミュレーションより得られた膜厚分布をRC抽出ツールにインターフェイスすることで、より実ウェハに近いRC抽出が可能になります。図10に膜厚ばらつきをルールテーブルで設定した場合とCMPモデルの結果を使用した場合のタイミングへの差分を示しています。右表に示されているように、パス1とパス2は、ルールテーブルではOKですが、CMPモデルではタイミングが悪化しています。レイアウトによる膜厚のばらつきといったシステマティックなばらつきを考慮することで、設計マージンを減らし、よりチップ性能を引き出す設計が可能になります。(図11 参照)

図10: 膜厚ばらつき考慮のRC抽出とタイミング解析

図11 : 設計マージンの改善

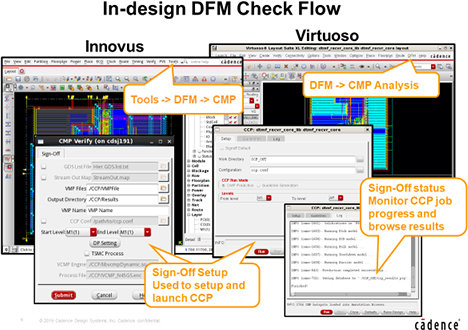

CMP検証のケイデンスツールへの統合 : In-Design DFM

設計段階で配線ばらつきを考慮するために、ケイデンスの設計ツールCadence Innovus™ Implementation SystemとVirtuoso™ Design Environment には、それぞれCCPを実行し平坦化チェックや膜厚考慮のRC抽出を行うIn-Design DFM機能を用意しています。図12にはDFMオプションのCMP機能の操作方法を示しています。Sign-off SetupウィンドウでCMPモデルを設定し、シミュレーションを実行すると、Sign-off Statusウィンドウに実行ログが表示されます。結果は、膜厚ばらつきの大きい個所をホットスポットとしてデザインに重ねて表示され、設計者でも簡単にCMPシミュレーションでのチェックが可能です。

図12 : Innovus/VirtuosoのIn-design CMPチェック機能

まとめ

高性能な半導体製造では、微細化だけでなく構造の複雑化が進み、プロセスエンジニアによる経験を基にした職人技だけでは早期立ち上げが難しくなっていきています。特に平坦化技術CMPでは、トランジスタ層から配線層までの積層での影響を考慮する必要があり、製造プロセス条件を最適化するだけでなく、CMP考慮のレイアウト調整が必須になります。平坦化が最適ではない場合、表面高さのばらつきはリソグラフィー工程でのDoF (Depth of Focus:焦点深度)ホットスポットを誘発し、配線層では抵抗と容量のばらつきによるタイミング悪化や、配線がショートするCuプーリングといった回路への問題が生じ、歩留り悪化の原因となります。ここでは、Cadence CMPソリューションを使用した、製造プロセスとレイアウト設計、両サイドからの平坦化アプローチについて紹介しました。

なお、2月26日に東芝メモリ様におけるCadence CMP Process Optimizerの採用事例についてプレスリリースを発表させていただきました。併せてご参照下さい。

フィールドエンジニアリング&サービス本部

デジタル&サインオフ

市川 仁子

この記事に関する問い合せ先:

コーポレート・マーケティング部

E-mail:cdsj_info@cadence.com

Latest Issue

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues