Joules RTL Design Studio ~ 完全に最適化されたRTLを迅速かつ高精度に実現

従来から、フロントエンド側RTL設計とバックエンド側インプリメンテーション設計間では、役割分担がおこなわれていたため、設計初期に電力、パフォーマンス、エリア、および配線混雑度等、PPAC(Power, Performance, Area, Congestion)の現状を可視化できないという課題は、ほとんどの場合対処できていません。RTL設計者はこの課題に定期的に直面しており、その結果、重要なタイミングと配線混雑の問題を解決する必要がある段階でソースコードを迅速にデバッグできません。このためRTL設計者とインプリメンテーション設計者の両者の間で余分なやり取りが発生し、チームの負担が大きくなり、設計サイクルが延長され、市場投入までの時間が大幅に遅れてしまう問題がありました。設計チームが競争力のあるスケジュールを守り、差別化された製品を期限までに市場に投入するには、RTLをインプリメンテーション設計チームに引き渡す前にタイミングと配線混雑度の主要な問題に対して正確な解析とインテリジェントなデバッグを実行できる機能が必要です。

Joules RTL Design Studio は、高品質なPPACを達成するためにフロントエンド設計者に対して最適化されたRTLハンドオフを可能にする環境を提供します。このソリューションによるPPACの見積もり結果は、ケイデンスの Innovus Implementation System、 Genus Synthesis Solution、およびJoules RTL Power Solution のコアエンジンを搭載し、きわめて信頼性の高い結果を使うことでユーザーは設計上の品質判断のために結果を信用できるようになります。さらに独自のインテリジェントなデバッグ アシスタント システムにより、デザインのPPAC違反の考えられる要因が優先順位付けされ、設計者がRTLの問題に対処する方法を理解できるようになり、よりスマートで効率的な製品の実現につながります。

また、Joules RTL Design Studio は、生成AI ソリューションである Cadence Cerebrus Intelligent Chip Explorer と緊密に統合し、フロアプランの最適化や周波数と電圧のトレードオフなどの様々な設計シナリオを検討したり、 Cadence Joint Enterprise Dataと AI Platformの統合により、異なるバージョンの RTL または以前のプロジェクト世代にわたる傾向と解析の分析が可能になるように現在開発側が取り組んでおります。

Joules RTL Design Studioの特長と利点

- ユニークなインテリジェント RTL デバッグ アシスタント システム

- デザインのPPAC結果を早期に提供するとともに、RTL設計からインプリメンテーション設計までのフローを通して実用的なデバッグ情報も提供します

- 設計イタレーションを最小限に抑えて製品のPPAを向上させるために、設計者は複数のシナリオと潜在的な解決策に対してwhat-if解析を実行可能です

- RTL で結果の品質 (QOR) が最大 25% 向上します

- RTL とインプリメンテーションデータベースの両方の入力をサポート

- フロントエンド設計者がインプリメンテーション設計者のデバッグを直接支援することでインプリメンテーション設計の課題を解決できるようになります

- 実績のあるエンジンをベース

- Joules RTL Design Studio は、Innovus Implementation System、Genus Synthesis、Joules RTL Power Solutionの信頼できるエンジンを共有しているため、信頼できるプロトタイプの精度を実現します

- TATの短縮と生産性の向上

- 高速なインプリメンテーション結果の予測、および高速化された処理時間により、通常のプロダクション合成フローと比較して、最大5倍の生産性向上が可能です

- インテリジェントな解析結果のフィードバックにより、より高速かつ少ないイタレーションで作業が可能になります

- 統合されたコックピットによる高度な RTL 設計環境

- RTL 設計者に効率的かつ使いやすい解析環境により、インプリメンテーション結果のフィードバック、違反の特定と分類、ボトルネック解析、RTL、回路図、レイアウト間のクロスプローブを提供します

- 最適なPPAのためにすべての解析とデザイン探索機能はシングルコックピットのGUIから実行可能です

- 高度な RTL 設計機能

- RTL Restructuring – 論理階層を変更します。インスタンスをグループ化、グループ解除、移動、追加、または削除し、修正されたRTL を出力します

- Track PPAC – 設計ステージ間で QoR を比較します

- RTL Diff - 単純な RTL の変更から複雑なロジックの変更まで、様々な抽象化レベルでの RTL の差分をハイライト表示します

- リントチェッカーの統合

- 設計者がリント チェッカー (デザイン、スイッチングアクティビティ、UPF、インプリメンテーション制約、SDC制約などのチェック) を段階的に実行して、データやセットアップの問題を事前に除外し、エラーと完了までの時間を削減できるようにします

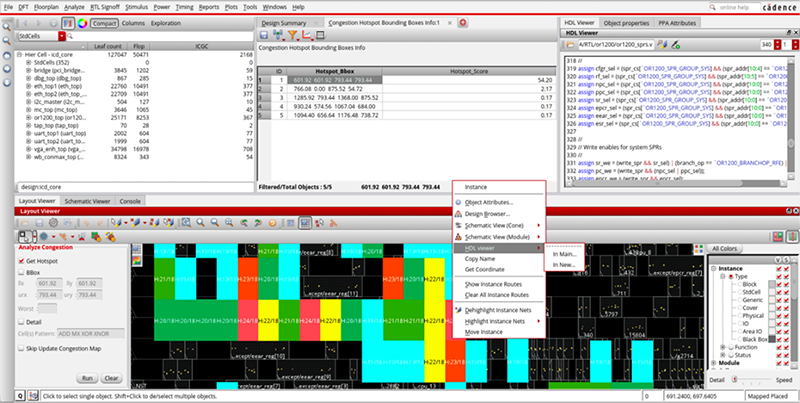

図1 HDLクロスプローブを備えたインタラクティブな配線混雑レイアウトビューア

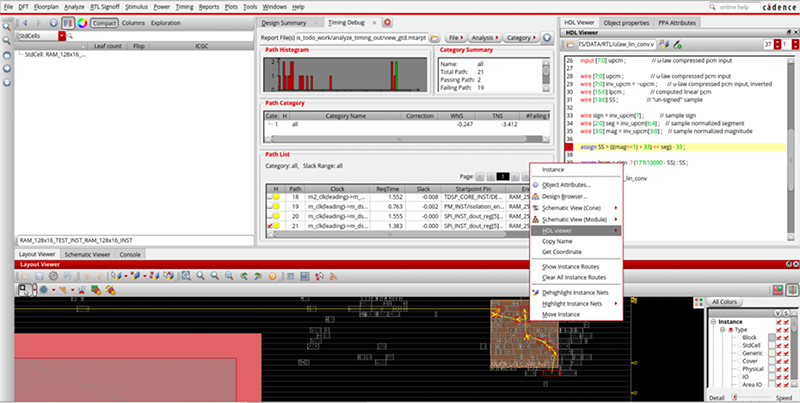

図2 HDL クロスプローブによるタイミング デバッグ

まとめ

Joules RTL Design Studio はCadenceのデジタル設計のコアエンジンを搭載し、統合された解析環境により最大5倍の生産性向上及び25%のRTL品質向上が可能なRTL設計環境を提供します。RTL設計課題解決に寄与できるJoules RTL Design Studioを是非ご体験ください。

フィールドエンジニアリング&サービス本部

デジタル&サインオフ

野原 秀公

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues