Virtuoso Studio IC23.1を使ってアナログ・ミックスシグナルIC設計を効率化

Virtuosoプラットフォームは業界標準のアナログ・ミックスシグナル設計ツールであり、30年以上に渡り世界中の多くのお客様にご利用いただいております。その最新バージョンであるVirtuoso Studio IC23.1が2023年6月にリリースされました。前バージョンのICADVM20.1は2020年にリリースされていますので、約3年ぶりのメジャーバージョンアップとなります。

この記事ではVirtuoso Studio IC23.1のレイアウト関連の機能について、主なアップデートや追加された新機能等を簡単にご紹介します。

◼️基本コマンドに対する継続した改善及び機能追加

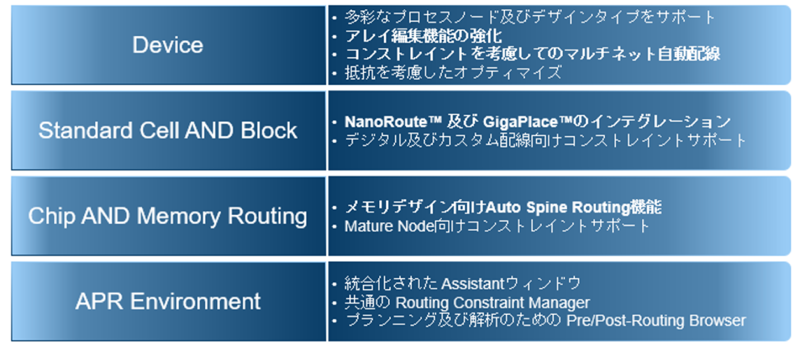

現在のVirtuosoのベースとなっているIC61シリーズがリリースされてから、既に15年以上が経過しています。今回IC23.1のリリースに合わせ、レイアウト設計作業を行う上でベースとなるコマンドのコードの見直しやアーキテクチャの作り直しを行い、パフォーマンスの改善とマルチスレッド化が図られました。また、図[1]に示すレイアウト設計の生産性を向上させるユニークな新機能や、VLSの上位機能を使うための基となるXL Complianceを満たす状態を保つためのアシスト機能、マニュアル配線や半自動配線に関する新機能など、様々な新機能が搭載されています。

図1:Core編集分野における改善と新機能

◼️レイアウト自動化機能 APR (Automated Placement and Routing)

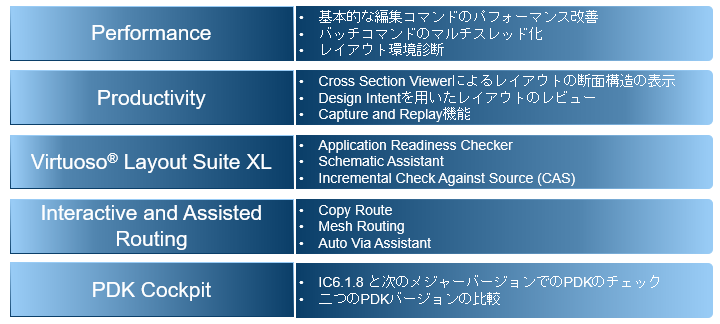

APRフローはVirtuosoのレイアウト自動化機能群を統合した自動化フローです。アナログ・ミックスシグナルデザインにはDevice Level, Standard Cell and Block, Chip Assembly and Memory Routingなど、いくつかのデザインスタイルがあり、それぞれのスタイルで求められるレイアウトの特徴/品質が異なります(図2)。 そのためVirtuosoにはいくつかの配置配線エンジンが用意されていますが、過去のバージョンではそれぞれのエンジンに対して設定の仕方や操作方法等が異なっていたため、ある程度自動レイアウトの経験を積んだユーザーでないと機能を使いこなすのが難しい状況でした。今回リリースされたIC23.1ではこれらの自動化機能群が一つのAPR環境に統合され、ユーザーは一つのGUIから事前設定をするだけで、あとはツールがそのデザインに最適なエンジンを選択してくれるため、自動レイアウトの経験がないユーザーでも簡単に自動レイアウトを実行できるようになりました。

図2:各デザインスタイルと必要な自動化機能

◼️アナログマイグレーション機能

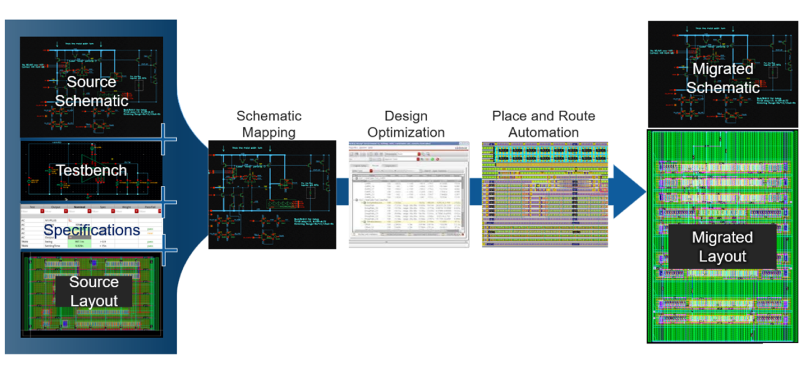

既存のデザインを1,2世代先の微細化プロセスにマイグレーションしたい、というケースは非常に多いと思います。IC23.1に搭載されたアナログマイグレーション機能は回路図も含めデザインのマイグレーションに大きく役立つ新たなソリューションです(図3)。

図3:IC23.1 アナログマイグレーションフロー

入力として必要なデータはソースデザインのschematic、テストベンチ、Simulationスペックの指定、レイアウトです。これらのデータを使いschematicを自動的にターゲットプロセスのsymbolに置き換え、その回路を既存のデザインと同様の回路特性が出せるようADEのオプティマイズ機能を使って最適化を行います。レイアウトはソースレイアウトの素子配置情報を抽出してターゲットプロセスでも同様の素子配置位置を再現、そこからVirtuosoの自動化機能を使いレイアウトを完成させます。このマイグレーション機能を使うことで、ターゲットプロセスでスクラッチからデザインを作成するよりも遥かに短い時間でデザインを完成することができます。

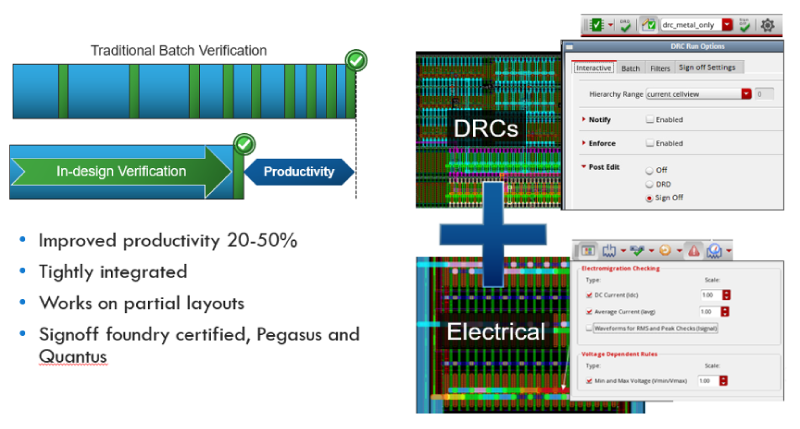

◼️In-Design Sign-off DRC/Fill機能とEAD New Re-Simulation Flow

Virtuoso上でSign-off DRCを実行する機能として、以前からPegasus Interactiveというツールが在りましたが、IC23.1では弊社のSign-off VerificationツールであるPegasusをよりタイトにインテグレートし、iPegasusとしてリニューアルしました。DRCの処理速度自体も以前より上がっていますし、レイアウトエディターに統合されたアシスタントにより、より結果解析もしやすくなっており、レイアウト設計の生産性向上に大きな効果が期待できます(図4)。

また、EAD (Electrically Aware Design) では、Re-Simulation向けの機能として弊社Sign-off LPE抽出ツールのQuantusを抽出エンジンとして使用できるようになりました。In-Designの寄生抽出でより高精度な結果を得ることができることや、以前のEADでは対応できなかったような大規模なデザインにも対応できることがこの機能のメリットです。

図4:In-Design検証による生産性の向上

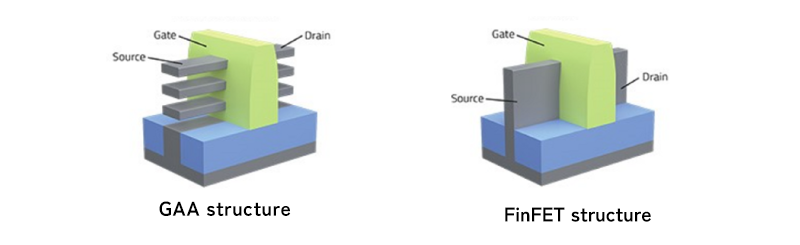

◼️GAA (Gate All Around) プロセスのサポート

2nm/3nmといった最先端プロセスではデバイスにGAA structureが採用され、より複雑なフィジカルルールに対応する必要が出てきました(図5)。

図5:GAAとFinFETのデバイス構造

IC23.1ではそれらの複雑なルールを全てサポートし、GAAプロセスでの設計が可能になりました。新たなデバイス構造もPCellのパラメータで全て表現しているため、レイアウト設計者はこの複雑なGAA構造を意識することなく従来と同じような感覚でレイアウト作業を行うことが可能です。

◼️まとめ

この記事では、Virtuoso Studio IC23.1でアップデートされた機能や、追加された主な新機能をご紹介しました。Virtuoso Studio IC23.1は皆様の設計の生産性を向上させ、高品質なデザインを作成するための様々なソリューションを提供できます。 また、Virtuosoプラットフォームは日々機能拡張を続けており、AI/MLを使った回路最適化機能やレイアウト生成機能の開発も進んでいます。今後のIC23.1シリーズの進化にもご期待ください。

◼️REFERENCES

- Virtuoso Studio IC23.1がリリースされました,Cadence Blog

- Virtuoso Studio: 最速よりも速く- 次の10年に向けたカスタム・プラットフォーム,Cadence Blog

- Virtuoso Studio: デザイン、プランニング、解析 – コインの3つの側面、エピソード1, Cadence Blog

- Virtuoso Studio: デザイン、プランニング、解析 – コインの3つの側面、エピソード2, Cadence Blog

- Virtuoso Studio: 正しい意図を持ってコラボレートしよう! ,Cadence Blog

フィールドエンジニアリング&サービス本部

カスタムIC&シミュレーション&SPB シニアAEマネージャー

五月女 和博

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues