Virtuoso ICADVM18.1 - 先進的メソドロジーご紹介

2018年10月に新しいVirtuoso、Virtuoso® ICADVM18.1 がリリースされました。

Virtuoso ICAVM18.1は、先端プロセスに対応しているだけでなく、従来プロセスにおいても大幅なTAT短縮を可能にする新しいメソドロジーを搭載しています。

その中でも特徴的な下記4つのメソドロジーについてご紹介します。

- Simulation Driven Layout

- Design Planning and Congestion Analysis

- Concurrent team design

- Design intent

(1) Simulation Driven Layout

Virtuoso ICADVM18.1には、業界初となるSimulation Driven Layout と呼ばれる新しい設計手法が加わりました。これは、Simulation の結果をLayout作成時に反映し、Layoutの初期段階からEM/RC制約を満たす適切な幅の配線を作成する設計手法です。

従来の設計手法Electrically Aware Design (EAD)では、Layout 作成後にEM / RC チェックを行いますが、新しいSimulation Driven Layoutでは、Layout作成時にリアルタイムにEM/RCを考慮でき、EM/RC制約を満たす配線を作成できるようになります。

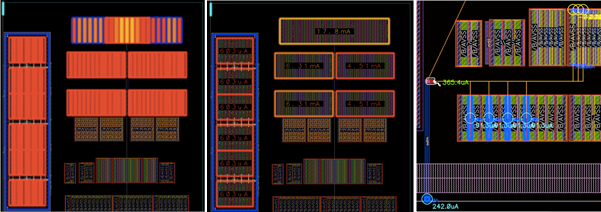

下の図は、Simulation の結果をLayoutに反映した様子を示しています。

左の図は、あるネットの電流密度をカラーマップで表示しており、中央の図は、各配置のかたまりが消費する電流値を表示しています。

また、右の図では、Create Wire の実行中に、リアルタイムに各ピンの消費電流が表示されている様子を示しています。

このように、Simulation の結果をLayoutに反映することで、EM/RCを考慮したLayout設計が可能になり、EM/RC制約を満たす配線を作成できるようになります。

そして、LayoutからSimulationへのイタレーション回数が削減できTAT短縮が可能になります。

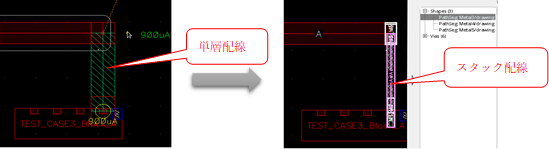

また、Simulation Driven Layoutにより下記のような配線が可能になります。

(2) Design Planning and Congestion Analysis

アナログカスタムIC設計において、Top-Downフロー、 Bottom-Upフロー、どちらにおいてもチップのプランニングはとても重要で、多くの場合、プランニングには、何度も修正を行い、非常に多くの時間がかかります。

ICADVM18.1 では、新しい効果的なプランニング手法を提案いたします。

- Virtual Hierarchy

階層構造や実際のブロックを持たない設計初期段階においても、 仮想階層 ”Virtual Hierarchy” を用いることで階層構造・ブロックを考慮したプロアプランを行うことが可能になります。

- 配線混雑度の解析

配線混雑度の解析と配線経路の見積もりを、実配線を作成する前に行うことができます。

どの場所がどの程度混雑しているのかLayout上で確認でき、また、混雑度の分布をグラフで確認することもできます。この解析によって、適切な配線領域の確保や混雑箇所を回避する配線経路の構築が可能になります。

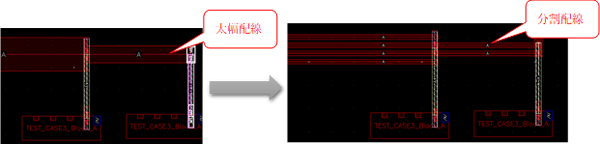

下の図は、Design Planner を活用した一例を示しています。

左図の中で、緑色で示されているのは “Virtual Hierarchy”です。階層構造は実在しなくても“Virtual Hierarchy”によって階層構造があるかのような扱いができ、効果的なプランニングが可能になります。

右の図では、配線の混雑度をカラーマップで表示し、混雑度の割合を棒グラフで示しています。

配線領域に余裕があるところは青色、やや混雑しているところは緑色、非常に混雑しているところは赤色で示しています。この解析により適切な配線領域の確保やフロアプランの最適化ができるようになります。

(3) Concurrent team design

チームワークによるLayoutの同時平行設計が可能となりました。

従来は、どんなに大きなLayout データでも、1人の設計者のみが編集・書き込みできる権限を持っていましたが、ICADVM18.1では複数のユーザーが同時に1つのLayoutデータを編集できるようになりました。

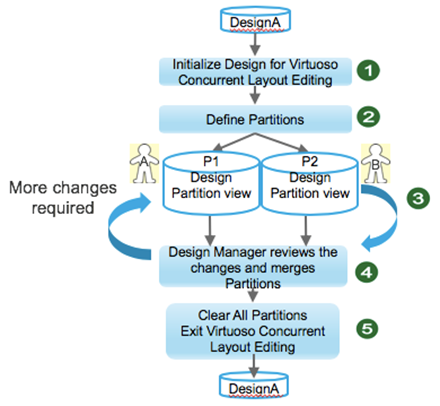

下の図ではそのイメージを示しています。1つのLayout Cell viewをパーティションで区切り、各パーティションをそれぞれの設計者が編集します。最後に区切られたパーティションをマージするフローとなります。

Chip Finishing や、DRC Fixing のTAT 短縮に大きく貢献する機能です。

(4) Design intent

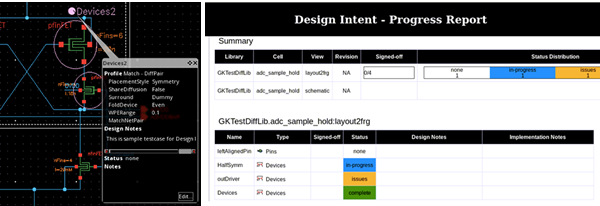

Design Intent は、設計要件や設計制約を、回路図からLayout にスマートに受け渡す機能です。従来は、テキストなどを使い回路設計者からレイアウト設計者に設計制約等を伝えていましたがDesign Intentの機能によって、効率良く設計制約を伝えることができるようになりました。

また、その制約が守られているかどうかレポートする機能もあります。

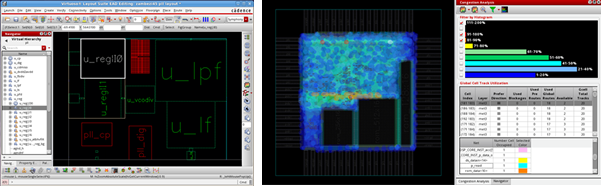

左下の図は、Design Intent機能を使って回路図上のデバイスに制約を付加した様子を示しており、右下の図では、その制約がLayout上で守られているかどうかのレポート結果を示しています。

以上、ICADVM18.1に搭載された新しい4つの機能についてご紹介しました。

その他にも、ICADVM18.1 は、5nmプロセスの設計に必要な機能も搭載しております。

設計の効率化に大きく貢献する ICADVM18.1 を是非お試し下さい。

なお、今回ご紹介しましたICAVM18.1の新機能を含め、大幅に機能改善が行われた新バージョンVirtuoso 6.1.8について詳しくご紹介するためのセミナーを11月29日(木)、イノテックビル・セミナールーム(新横浜)において開催する予定です。是非ご出席いただけますようお願いいたします。

セミナーの詳細・お申し込みサイトは弊社ホームページにて近日中に公開いたします。

フィールドエンジニアリング&サービス本部

内藤 美紀

コーポレート・マーケティング部

E-mail:cdsj_info@cadence.com

Latest Issue

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues