新時代の幕開け、アドバンストメソドロジ対応ツール Virtuoso ICADVM18.1

先端テクノロジを使用して設計をする際、ユーザーが実際に直面する問題は、複雑な新しいプロセスノードの要求を満たすことに加えて、多くの異なる部分から構成させれる複雑かつ多機能な製品の開発を行うことです。つまり、先端テクノロジにおいては、非常に高速な動作やデータ転送が要求されるようなRF(Radio Frequency:高周波)動作回路や、フォトニクスインターフェースが含まれることになります。

ケイデンスは、このように先端テクノロジに見られがちな、多岐に渡る設計要求が混在する状態に対応するため、従来の先端テクノロジ向けVirtuoso® ICADV12.3 の機能を大幅に向上させた上位互換ツール、Virtuoso® ICADVM18.1 を2018年10月にリリースいたします。

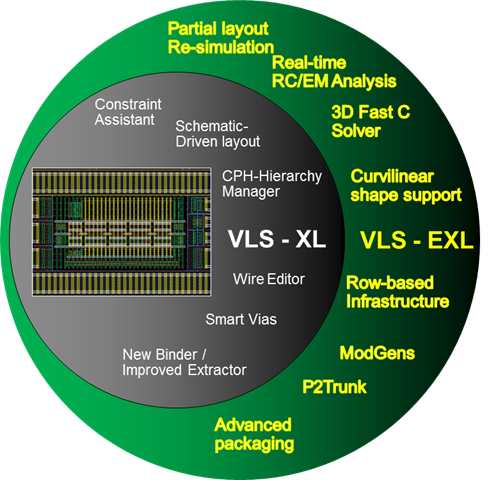

このVirtuoso ICADVM18.1は、アドバンストメソドロジ対応開発環境として位置づけられ、先端ノードに加え、フォトニクス、RF設計環境、アドバンストパッケージング等の、多くの新機能が実装されます。これらは、新規にリリースされるVLS-EXL プラットフォーム上の、Electrical Driven 環境で統合されます。(図1)

図1.VLS-XL とVLS-EXL プラットフォーム

EXL プラットフォーム上で利用可能になる主な機能は以下の通りです。

- 5nm プロセスノード対応、開発環境

- Electrical Driven環境上で動作する自動、半自動、及びマニュアルでの設計環境

- より機能強化されたリアルタイムEM解析、modgen、 P2T, T2T, Trunkgen 機能

- フォトニクスデザイン、RFデザインで要求される曲線図形のサポート

- ハイエンド・アドバンストパッケージングのサポート

Virtuoso ICADVM18.1 は非常に豊富な機能で構成される、総合開発プラットフォームです。各新機能については、後日、追って紹介していきますが、今回は特に、リリースに先立ち、先端ノードに関連する新機能のいくつかについて紹介します。

5nm node support

5nmのプロセスノードにおいては、更にデザインルールが複雑化します。例えば、特定エリアとその周辺で異なるルールが適用されるarea based rules、SADP で必要になるtrim rules、特定のパターンに適合するviaに対して適用される複雑なvia ルール、base layer のutilization rules等がそうですが、これらは、10nm, 7nm の延長線上にあり、ICADV12.3 にて、実装が完了している機能群(Row Based Placement, WSP等)で基本的に対応できています。

Virtuoso ICADVM18.1 では、新しいテクノロジファイルの拡張サポートに加え、後述するSimulation Driven Routing, 更に機能強化がなされたcoloring 機能等のDynamic Editing 機能により操作性が更に向上します。

SDR (Simulation Driven Routing)

Virtuoso ICADVM18.1 で利用可能になる新機能にSimulation Driven Routing があります。この機能は、配線中に、実際の電流値をリアルタイムにモニタしながら配線を行うことを可能にする非常にパワフルな機能です。

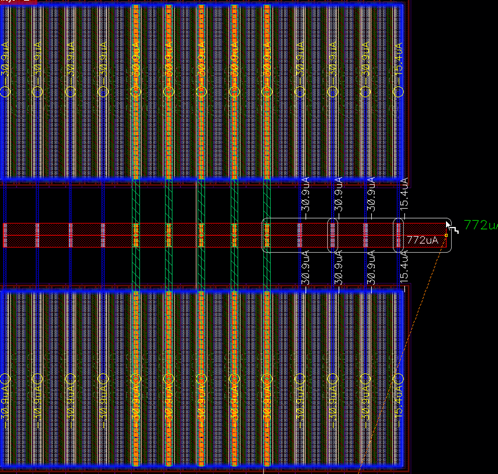

図2に示す例では、幹線(trunk)を配線中、自動的にviaを落し、各ノードに配線を行っています。M2(赤)のtrunk を横方向に、左から、右に配線しています。各デバイスへのtwig (小枝という意味です)で消費される電流値がリアルタイムに表示され、どの部分でどの位電流が消費されるかが容易に確認できます。

図2.SDRを使用したtrunk からのtwig への配線 I

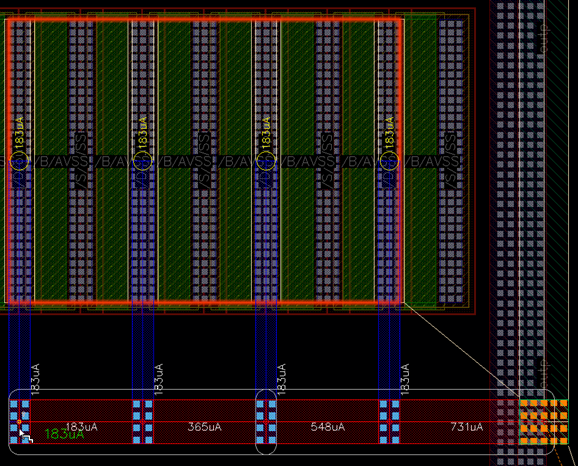

また、以下の図3の例では、M2(赤)のtrunk を今度は逆に、右から、左に配線しています。各デバイスへ配線がなされるたびに、trunkの電流値が減少していることに注目してください。

Advanced Nodeではこのように、ツールによるデザイン作成中でのダイナミックなフィードバックが、TATを短縮する鍵となります。

図3.SDRを使用したtrunk からのtwig への配線 II

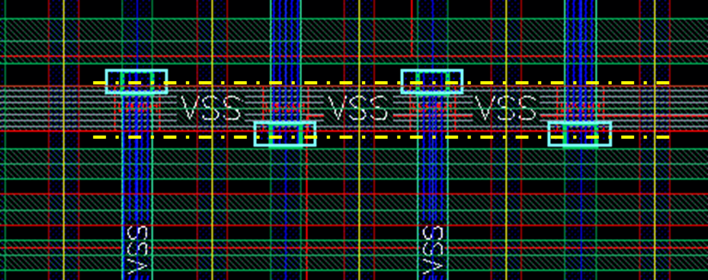

Metal Fill

7nmノード以降で多く採用されているSADPアーキテクチャは、配線に使用される配線用のリソースを、あらかじめ全て用意しておいて、配線に必要な部分とそうでない部分の間をカットして、必要な部分だけ使用します。(このカット部分の「きりしろ」の事をTrim Shapeといいます。)従って、配線の出来上がったシリコン上には、配線に使用されていない未使用配線部分が残っています。デザイン上での、この残った部分に対する処理は、ファウンダリやテクノロジによりさまざまなのですが、使用するテクノロジによっては、これらの未使用配線をも、レイアウト上に実現した状態でのテープアウトが要求されます。Virtuoso ICADVM18.1 はSADP での使用に好適なWidth Spacing Pattern (WSP) を利用したmetal fill 機能を実装し、ファウンダリからのさまざまなmetal fill の要求を満たします。

WSPとは、簡単に言うと、デザイン内に、あらかじめ定義する配線トラックの事で、デザイン中の任意のエリアに異なる配線トラックのパターンを定義して使用できる機能です。

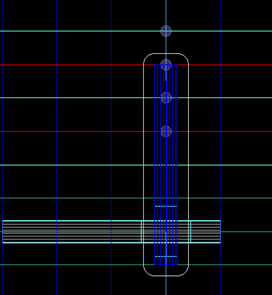

特に、trim shape 間の複雑なデザインルールを満たすため、直行する配線レイヤの配線グリッド(WSP)を参照するOrthogonal Grid Snapping 機能を実装し、trim shape 間のエラーを軽減し、metal fill 後のエラーの発生を抑制しています。

図4.orthogonal grid を使用したマニュアル配線例

図5.orthogonal grid を用いたtrim shape の挿入とmetal fill

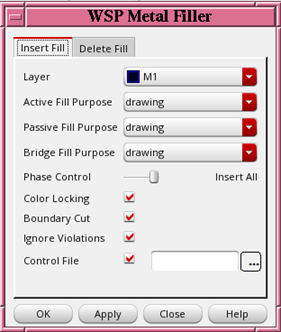

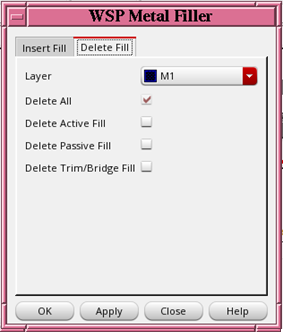

図6(a), (b)に、Virtuoso ICADVM18.1 で実装される開発中のMetal Fillerのfill 挿入、削除GUIを示します。

図6(a).WSP Metal Fill GUI -I |

図6(b).WSP Metal Fill GUI -II |

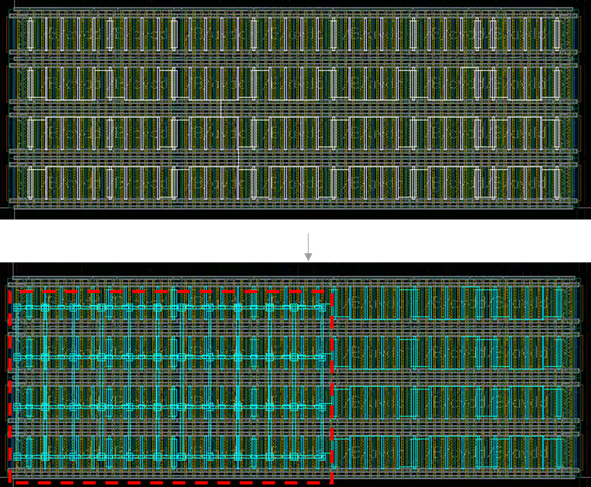

Trunk Gen

Trunk Gen は、レイアウト中に幹線(trunk)を自動的に生成する機能です。

Pin2Trunk (各ピンと幹線を自動接続する機能)、Trunk2Trunk(複数の幹線を自動接続する機能)と組み合わせることで、tree 構造の配線が自動で行えるようになります。WSPとの併用で威力を発揮するSADPでの配線に好適な半自動配線機能です。

既存の自動配線機能と併用することで、大幅な配線作業の簡素化が計れます。

図7.Trunk Gen 前(上)と、Trunk Gen 実行後(下)*赤枠内にtrunk (幹線)を発生し接続

Coloring Enhancement

2018年になり、いよいよ波長が13.5nm のEUV (Extreme Ultra-Violet)が実用化される様になりました。一時は複数のマスクを使用するmulti-patterning はもう不要になるといわれていましたが、EUV が登場してもなお、カラーリングのニーズはなくなっていません。ケイデンスは、従来のカラーリング機能を更に強化し、Virtuoso ICADVM18.1で、多くの新機能を実装しています。

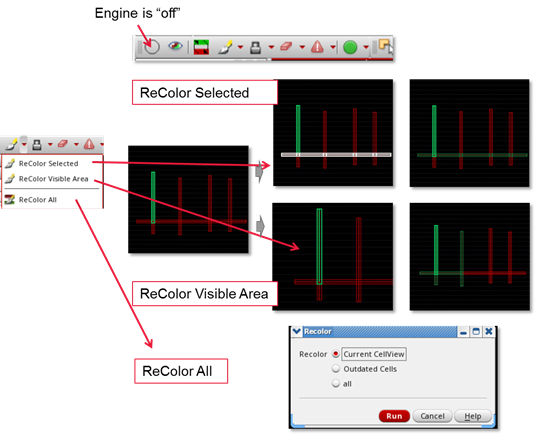

例えば、大きなデザインを開いた際、自動的にカラーリングがスタートしてしまい、パフォーマンスの問題につながるというものがありましたが、coloring の対象となるエリアや、レイヤ等を選択できるようにエンハンスすることで、このような問題を解決しています。(下図ReColor ダイアログ参照)

図8.OnDemand Coloring

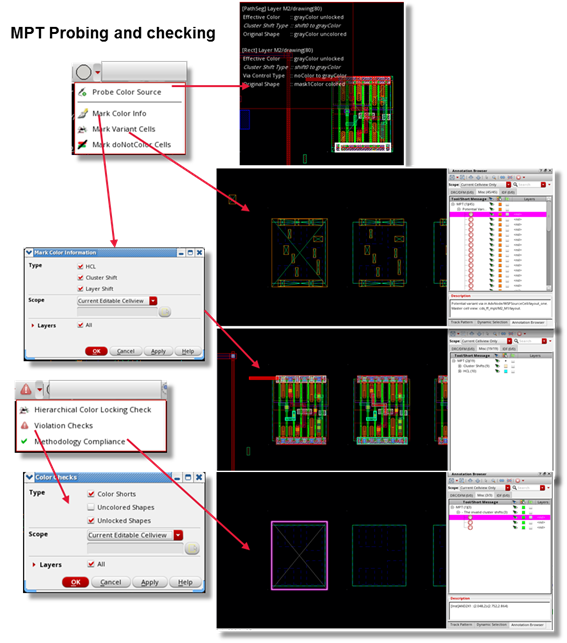

そして、複数の階層により構成されるデザインの場合、coloring method が混在し、どうして現在の色に配色されたのかを解析が困難になる場合がありました。Virtuoso ICADVM18.1 では、Color Debug, Color Probingを装備し、どのような状況で現在のカラーリングの結果になったのかを即座に解析できるよう工夫がなされています。

図9.MPT Probing とColor Checking

まとめ

設計効率化は誰もが求めるものですが、先端テクノロジでの製品開発で最も重要なのは、多くの複雑なテクノロジの要求事項に惑わされること無く、ユーザーが、如何に開発する製品の仕様の実現に集中できるかということにあります。Virtuoso ICADVM18.1の大きな特徴は、先端テクノロジを利用することにより、足かせになるような複雑な要求事項をシームレスなインターフェースにより吸収し、設計の効率が、更に向上するよう、多くの工夫がなされているところにあります。

これらは、SDRのようにリアルタイムにシミュレーション結果を配線中に表示するような、マニュアル操作のサポート機能に加え、Trunk Gen のような半自動配線、そして、全自動配線を必要に応じて使い分けることが出来るよう、柔軟かつ豊富な機能群が用意されています。また、今回は割愛しましたが、デバイスの配置についても、アナログデバイスの配置制約条件を、回路図から継承し、マニュアル、そして、自動での配置機能が利用可能です。

Virtuoso ICADVM18.1で実装される機能は全て、7nm, 5nmといったプロセスノードだけではなく、16nm, 14nm といったプロセスノードでの設計の際にも、非常に有効に機能します。

Virtuoso ICADVM18.1は、先端テクノロジによる設計の際に必要となる全ての部分を網羅する先端テクノロジ開発用のアドバンストメソドロジ対応ツールです。

石川 浩

Sr. Engineering Manager, CPG

米国ケイデンスデザインシステムズ

This article is for information purpose only and does not represent a commitment to deliver any of the features or functionality.

本稿中で紹介している新機能は、開発中であり、予告無く仕様等が変更される事があります。

コーポレート・マーケティング部

E-mail:cdsj_info@cadence.com

Latest Issue

- ハイパフォーマンス・コンピューティングとコンシューマ機器に向けた次世代のメモリ規格DDR5に対応するケイデンスのIP

- CDNLive Japan 2018開催のご案内

- 編集後記

- Innovus 18.1: 待望のメジャー・アップデート、遂にリリース! ~業界をリードするデジタル設計ソリューションの新機能を搭載~

- Tempus-ECO ver.18.1最新機能のご紹介 ~ Multi-Level Clock Skewing ~

- ダミーフィルの影響をインデザインで解消 – Virtuoso IPVS SignOff Fill & Density Analysis

- アナログIC用信頼性考慮設計ソリューション「 Legato Reliability Solution 」

- 車載電子システム向け機能安全メソドロジ

- オートモーティブ電子システムデザイン・セミナー開催レポート

- 東アジアのお客様は英語の資料を要求してきましたよ

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues