ダミーフィルの影響をインデザインで解消 – Virtuoso IPVS SignOff Fill & Density Analysis

先端プロセスノードに於けるデザインルールは複雑さを加速度的に増しており、設計者はエンドユーザーが求める納期に合わせて設計を完了することがより困難になってきています。特に先端ノードのレイアウト検証では、デバイスや配線の幅や間隔のチェックだけでなく配線密度違反の解消にも時間を取られ、レイアウト工程の足かせとなりつつあります。例えば、

- 配線密度ルールにおいて各配線層に対するチェックウィンドウは世代が進むにつれ狭まり、小さな領域でも一定の密度を保つ必要があるため、時にはレイアウトの自由度を阻害することがあります。

- 配線プロセスの平坦化に留まらず配線線幅の仕上がりを改善するためにOPC(Optical Proximity Correction)用途のダミー図形が配線の近傍に挿入されるため、ダミーフィルによる配線間容量への影響が増大しています。

- デバイスダミーに於いても、近傍に配置されるポリシリコンや拡散図形との間隔も回路性能への影響度を増しています。

- また、チェックウィンドウの原点位置が変わるためにカスタムIPの配置位置によりトップ階層で密度違反が発生することがあり、カスタムIP内のダミーフィルを調整して密度違反を解消することが必要になることがあります。

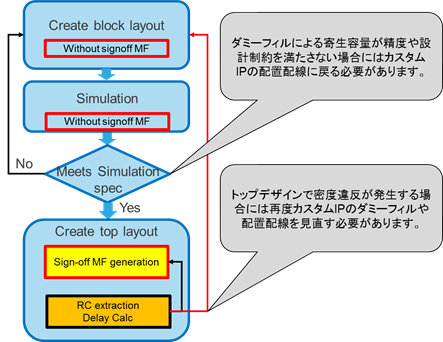

図1: 従来設計フローでの大きな出戻り

このため、従来は設計の後工程で挿入されていたデバイス及び配線のダミーフィルをカスタムIPの設計早期の段階で実施して、回路性能、設計制約に対して満たされているか確認しながら進めることが必須となってきています。

ケイデンスは、レイアウト検証の課題を解決するソリューションとして、Cadence® Virtuoso® Integrated Physical Verification System (IPVS) をリリースし機能を拡充してまいりました。そして今回、このダミーフィル問題を軽減するためのVirtuoso IPVSの2つの新機能を以下にご紹介します。

Virtuoso IPVS SignOff Fill *1

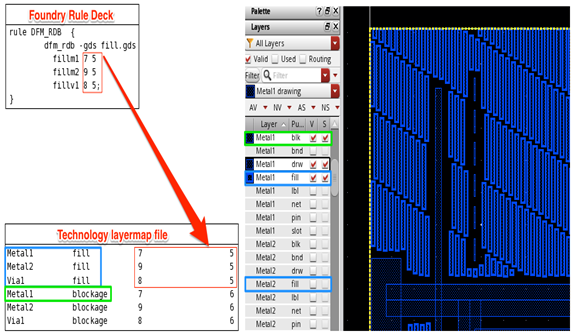

Virtuoso IPVS SignOff Fillはファウンダリが提供するルールファイルを使ってVirtuoso Layout View上に自動でダミーフィルを生成します(図2)。ダミーフィルのポリゴンデータはインスタンスとしてOpen Access(OA)に直接インポートされ、Virtuoso上でのStream-Inの実行やMosaic(Array Structure)を編集する等の手間は必要ありません。Virtuoso Layer Paletteと連動した限定レイヤのみ、また限定エリアのみのダミーを挿入する機能、そして逐次的にダミーを挿入する機能を備え、回路性能に支配的なクリティカルネット近傍の配線ダミーを除去する等のトリミングが容易に行えるフローを実現できます。

図2: Virtuoso IPVS SignOff Fill実行例

Virtuoso IPVS Density Analysis *1

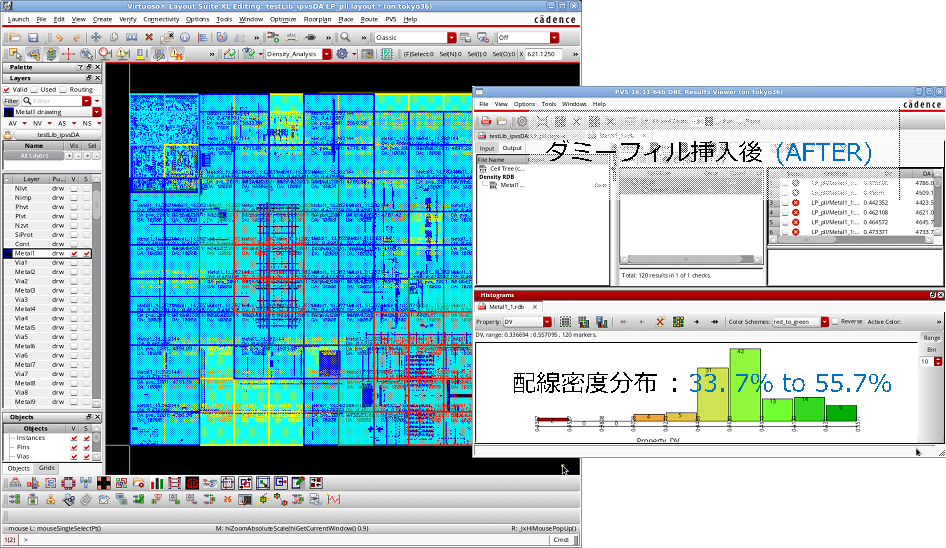

ファウンダリのデザインルールチェックは違反した箇所しか情報が表示されないため、密度違反の結果を解析しづらい課題がありました。Virtuoso IPVS Density Analysisはレイアウト内の全ての領域の配線密度を0から100%の分布に分け、かつ任意のチェックウィンドウ毎に表示する機能です。ファウンダリのルールファイルを用意する必要はなく、Virtuoso IPVSのGUI上で設定するだけで即座に密度分布を確認することができます。なお密度分布の状況はPVS Results Viewerにて表示されます(図3)。

図3: ダミー挿入後の密度分布例

PVS Results ViewerはPVS DRC Debug Environmentの後継ツールとしてv16.1から導入されました(*2)。PVS Results Viewerは高速かつ、大容量のエラーデータの処理が可能で、Virtuoso IPVS Density Analysisが出力するエラーデータからデバイスや配線レイヤの密度分布を即座に表示することができます。

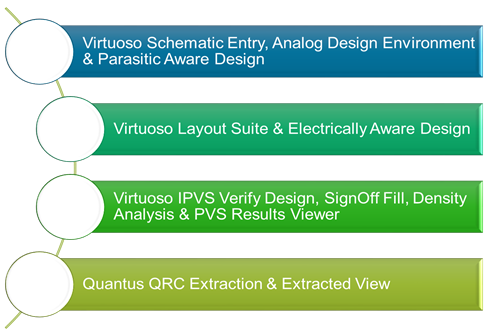

図4:Virtuosoインデザインソリューション

Virtuoso IPVSの各機能は全てVirtuoso Layout Suite上で動作し、Virtuoso IPVS Verify Designでデザインルール違反を解消しつつ、SignOff Fillでダミーフィルを挿入し、Density AnalysisとPVS Results Viewerで密度分布を確認できます。さらにその後Quantus QRC Extractionによる寄生RC抽出と、Virtuoso Parasitic Aware DesignやVirtuoso Electrically Aware Designによる寄生RC解析まで一貫してVirtuoso Layout View上で進められます。

本機能をこれらのツール群と連動して使用することにより、下位階層のデバイスや配線図形の粗密、そしてダミー禁止領域の影響を早期に把握して、上位階層のレイアウト時に密度違反が起こらないように設計を進めることが可能になります(図5)。またクリティカルネット付近のダミーフィルを調整し、配線の寄生容量を見積もりながら、レイアウトを修正することが容易に行えます(図6)。

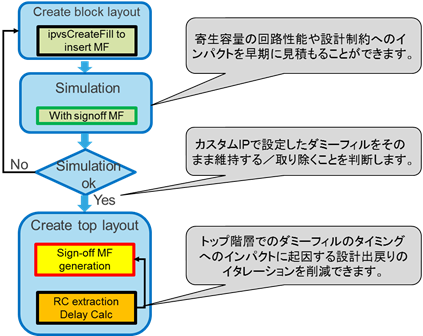

図5: ダミーフィル考慮設計フロー

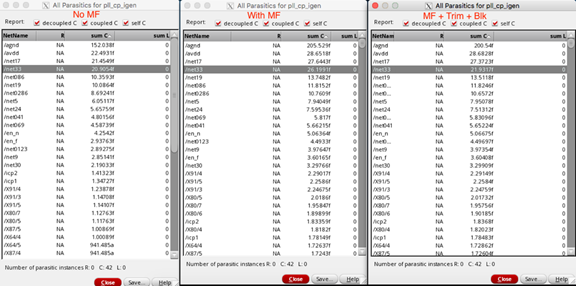

図6: 配線容量解析レポート比較例(Parasitic Aware Design)

※図6の例は、左からMF(配線ダミー)なし、MFあり、MF+Trim(配線除去)+Block(配線禁止) のネット毎の配線容量です。”net33”に着目すると「MFあり」から「Trim+Blk」の処理を加えることで26.1991fから21.9317fまで容量値を改善できました。

Virtuoso IPVSはデザインルールチェックだけでなく、ダミーフィルと密度計算の自動化の機能を備えるようになり、レイアウト作成から寄生RC抽出、シミュレーションまでのシームレスなカスタムIP設計フローを実現します。是非ご活用ください。

*1:2018年6月現在Virtuoso IPVS SignOff Fill及びDensity Analysisは限定ユーザーリリース(Early Access Programでのご提供)となっております。

*2:PVS Results ViewerはThe Sound of Cadence Online Vol.25に掲載しております。併せてご参照下さい。

フィールドエンジニアリング&サービス本部

阿久津 滋聖

この記事に関する問い合せ先:

コーポレート・マーケティング部

E-mail:cdsj_info@cadence.com

Latest Issue

- ハイパフォーマンス・コンピューティングとコンシューマ機器に向けた次世代のメモリ規格DDR5に対応するケイデンスのIP

- CDNLive Japan 2018開催のご案内

- 編集後記

- Innovus 18.1: 待望のメジャー・アップデート、遂にリリース! ~業界をリードするデジタル設計ソリューションの新機能を搭載~

- Tempus-ECO ver.18.1最新機能のご紹介 ~ Multi-Level Clock Skewing ~

- 新時代の幕開け、アドバンストメソドロジ対応ツール Virtuoso ICADVM18.1

- アナログIC用信頼性考慮設計ソリューション「 Legato Reliability Solution 」

- 車載電子システム向け機能安全メソドロジ

- オートモーティブ電子システムデザイン・セミナー開催レポート

- 東アジアのお客様は英語の資料を要求してきましたよ

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues