Tempus-ECO ver.18.1最新機能のご紹介

~ Multi-Level Clock Skewing ~

今回は2018年5月にリリースされたTempus™ Timing Signoff Solution ver.18.1のECO新機能、「Multi-Level Clock Skewing」についてご紹介いたします。

Tempus-ECOをよくご存じない方のために、本編に入る前にTempus-ECOはどのようなことができるのか簡単にご説明いたします。

Tempus-ECOとは

Tempus-ECOは約6年前にリリースされた機能です。P&Rツールで最適化を行ったデザインに対して、サインオフ・レベルの精度でタイミング検証し、その結果に基づいてタイミング改善を行うという目的で開発されました。

リリース直後は「MS ECO」という呼び名でしたが、Encounter Timing System™ (ETS)からTempus Timing Signoff Solutionへツール名が変更されたことに伴い、途中で「Tempus-TSO」、最終的には「Tempus-ECO」と名称を改めました。リリース直後の「MS ECO」では、コマンドに設定できるオプションの数、すなわち引数は16個でしたが、その後、着実に機能追加を行い、最新版ver.18.1の「Tempus-ECO」で設定できる引数は64にまで増えています。

ver.18.1の「Tempus-ECO」でできる代表的な機能と特徴を一覧にすると以下のようになります。

| 修正・改善対象項目 | |

|---|---|

| タイミング (Setup/Hold/Recovery/Removal) | エリア(面積) |

DRV (max_transition/max_capacitance) |

リーク・パワー |

クロストーク・グリッチ・ノイズ |

ダイナミック・パワー |

| 特徴および機能 | |

|---|---|

サインオフ精度遅延計算・SI解析エンジン |

階層およびフラットのECOカード作成 |

分散処理およびコンカレントMMMC |

Master/Clone(繰り返しインスタンス)対応 |

Innovus上での実行およびスタンドアロン実行 |

SmartScope 階層ECO(*1) |

インプリツールと同じ“Common Timing Engine” |

Incremental最適化 |

グラフベース、パスベース最適化 |

Incremental最適化後のsetupリカバリ処理 |

修正不可時の理由を出力 |

Hold最適化中の“Surgical” Setup最適化 |

物理レイアウト考慮 (LEF/DEF入力) |

Clock SkewingによるSetup最適化 |

先端ノード対応のDRCクリーンな配置指示 |

リーク・パワーとダイナミック・パワーの同時最適化 |

配線混雑考慮 |

リーク、ダイナミック・パワー最適化の重みづけ |

配線経路直下バッファリング |

ダミー・ロード・セルによるHold修正 |

各End Pointへのマージン設定 |

SOCVベースの最適化 |

DRVルールへのマージン設定 |

最長実行時間の指定 |

クロックのDRV修正 |

|

手作業によるECO

多くの場合、配線収束およびタイミング収束に目処がついた時点で、自動P&R/ECOステップを終了し、DRC違反やタイミング違反を手修正していく段階に入ります。タイミング修正については、最終手段としてクロック遅延を修正することになりますが、数多くのSDCモードやコーナ条件のそれぞれでタイミングを満足させなければなりませんので、なかなか容易ではありません。時には、修正するタイミング・パスから分岐した複数のEnd Pointへの影響も考慮する必要がでてきます。これらを踏まえて、タイミング・レポートと対峙しながら、ECOカードを作ることになります。

この作業はデザイン規模が大きく、かつSDCモードやコーナ条件が多いと非常に労力を要する作業となります。また、複数パスのタイミング修正を行う際に、共通する適切なECO箇所を発見できれば、最小限の面積増加・消費電力増加で済みますが、解析が難しい場合は、それぞれのパス毎の対応となることも多々あります。

このような煩雑で難解な手修正作業を大幅に減らし、かつスマートなECOカードを簡単に作成できたら、設計効率が大幅に改善されるかと思いますが、皆様いかがでしょうか? Tempus-ECOは「Surgical Setup最適化」と「Clock Skewing」機能でお手伝いすることができます。

Surgical Setup 最適化

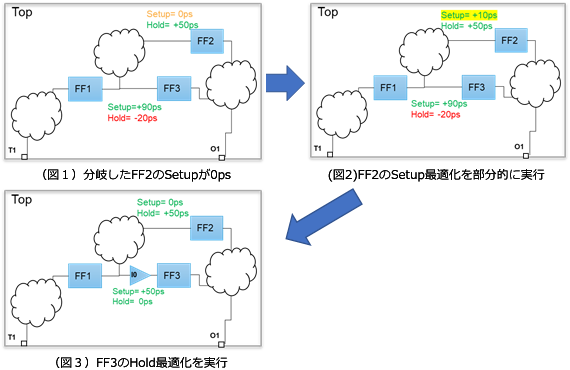

あるタイミング・パスのHold最適化を行う際に、該当パスから分岐している他方のEnd PointのSetupが辛うじてMetしているような状態においては、Hold最適化ができない場合があります。(図1)

ここではFF1とFF3のタイミング・パスのHoldのスラックが-20psとなっており、この点が最適化対象なのですが、分岐したFF2のSetupのスラックがちょうど0psとなっています。FF1とFF3の間にディレイ・バッファ挿入を行うと、配線経路や挿入したセルのピン容量の変化によってFF2でSetup違反となってしまう場合が想定されます。見積もりによって新しくSetup違反を生じてしまうような場合、Tempus-ECOはデフォルトでHold最適化を行いません。

Tempus-ECOはこのようなタイミング・パスを自動で検知し、先行してFF2のSetup最適化を部分的に実行します。(図2)

FF2のSetupに余裕を持たせた後に、FF3のHold違反を修正します。(図3)

このようなピン・ポイントのSetup最適化処理を腕の良い医者が行う外科手術になぞらえて、「Surgical Setup 最適化」や「Surgical ECO」と呼んでいます。

従来は手修正によって改善を行っていたこのようなタイミング・パスですが、Tempus-ECOでは処理をすべて自動で行わせることができます。もちろん、他のSDCモード条件やコーナ条件を考慮しての最適化です。

※この機能は2014年リリースのver.14.2よりサポートしており、お客様より大変好評を得ています。Tempus-ECOが選ばれる大きな理由の1つとなっています。

Multi-Level Clock Skewing (ver.18.1 新機能)

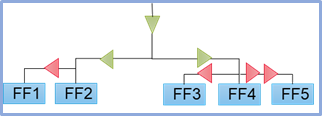

さて、ここからが本編となります。Clock Skew調整を行ってのSetupタイミング最適化は以前よりサポートしておりましたが、その手法は修正対象のFFの前段にバッファ挿入する方法のみでした。(図4)

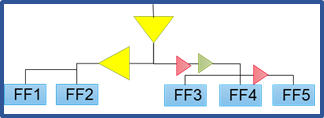

しかしながら、ver.18.1のClock Skewingではクロック・ツリーの中間でもバッファ挿入(インバータ・ペア挿入)や、バッファサイズの変更を行わせることができます。(図5)

これを「Multi-Level Clock Skewing」と呼んでいます。

(図4)FFの前段にバッファ挿入(赤)のみ

(図5)ツリー中間でのサイズ変更(黄)やバッファ追加

この機能により、より少ない面積増加で、より効果的なSetup最適化が実現できます。

いくつかの実例を以下にお見せいたします。

| Design 1: 1.8GHz High Speed Core |

WNS (ps) |

TNS (ps) |

違反 パス数 |

ECO 処理数 |

|---|---|---|---|---|

| 初期タイミング結果 | -11 | -30 | 6 | |

| 他社ツール | -6 | -9 | 2 | 400 |

| Multi-Level clock skewing適用結果 | 0 | 0 | 0 | 16resizes |

「Design 1」は1.8GHzで動作するハイスピード・コアです。こちらのお客様は他社ツールを用いて、Skew調整によるタイミング最適化を試行していましたが、わずか6つの違反に対して400のECOカードがを作成されましたが、タイミング違反を完全に取り除くことはできませんでした。ここでTempus-ECOのMulti-Level Clock Skewingを試していただいたところ、ツリー中間のバッファを16個サイズ変更するだけで、簡単にタイミング違反を取り除くことができました。

| Design 2: 3GHz High Speed Core |

WNS (ps) |

TNS (ns) |

違反 パス数 |

ECO 処理数 |

|---|---|---|---|---|

| 初期タイミング結果 | -17 | -1.93 | 755 | |

| Default clock skewing適用結果 | -15 | -9 | 453 | 2976 |

| Multi-Level clock skewing適用結果 | -5 | -0.11 | 86 | 2566 |

「Design 2」は3GHzで動作するハイスピード・コアです。FFの前段のみにバッファ挿入する以前の最適化手法と比較して、Multi-Level Clock Skewingでは更なる改善を少ないECO処理数で実現することができております。

まとめ

手修正による最適化が必要だったClock Skew調整を、ツリー中間でのバッファ挿入やサイズ変更も含めて、すべて自動で処理を行うことができるようになりました。

煩雑で長時間を要していた手修正によるタイミング改善を「Surgical ECO」や新機能「Multi-Level Clock Skewing」で大幅に削減することができます。

製品の市場投入までのリード・タイムを大幅に短縮できるTempus-ECOをこの機会にぜひお試しいただければと思います。

Tempus-ECOは他にもお役に立てる様々な機能を鋭意開発しております。今後、弊社Webサイトやセミナーなどで発信してまいりますので、よろしくお願いいたします。

CDNLive Japan 2018

(*1)Tempus-ECOの代表的な機能の中に「SmartScope™階層ECO」がございます。こちらは大規模デザインにおける階層タイミングECOのソリューションであり、デザイン収束性の向上と短TATを実現します。

本機能を用いた事例を2018年7月20日(金)に開催いたしますCDNLive Japan 2018にて、株式会社ソシオネクスト 共通テクノロジ開発統括部 第二設計技術部 清水俊仁様にご講演いただく予定となっております。この機会にぜひご聴講いただけますようお願いいたします。

CDNLive Japan 2018の詳細およびご登録はこちらからお願いいたします。

皆様のご参加をお待ちしております。

フィールドエンジニアリング&サービス本部

デジタル&サインオフ

小湊 丈寛

この記事に関する問い合せ先:

コーポレート・マーケティング部

E-mail:cdsj_info@cadence.com

Latest Issue

- ハイパフォーマンス・コンピューティングとコンシューマ機器に向けた次世代のメモリ規格DDR5に対応するケイデンスのIP

- CDNLive Japan 2018開催のご案内

- 編集後記

- Innovus 18.1: 待望のメジャー・アップデート、遂にリリース! ~業界をリードするデジタル設計ソリューションの新機能を搭載~

- ダミーフィルの影響をインデザインで解消 – Virtuoso IPVS SignOff Fill & Density Analysis

- 新時代の幕開け、アドバンストメソドロジ対応ツール Virtuoso ICADVM18.1

- アナログIC用信頼性考慮設計ソリューション「 Legato Reliability Solution 」

- 車載電子システム向け機能安全メソドロジ

- オートモーティブ電子システムデザイン・セミナー開催レポート

- 東アジアのお客様は英語の資料を要求してきましたよ

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues