Innovus 18.1: 待望のメジャー・アップデート、遂にリリース!

~業界をリードするデジタル設計ソリューションの新機能を搭載~

2018年5月、Cadenceのデジタル設計ソリューションを代表するフィジカル・インプリメンテーション・ツールInnovus™ Implementation Systemのバージョン18.1が、遂にリリースされました。Worldwideで積み重ねてきた最先端プロセスでの設計実績をベースに、配置、配線といった基本機能のアップデートはもちろん、革新的な新機能を数多く搭載しています。ここではInnovus Implementation System 18.1の代表的な新技術をまとめてご紹介いたします。

- Advanced node features and support

Innovus Implementation System 18.1は、日々進化する各社の最先端プロセスに対応し、配置や配線はもちろん、細かい設計ルールも完全にサポートしています。- 2.5D Padding

最先端プロセス設計の配線性にはセル配置によるpin densityの考慮が重要となってきています。2.5D Paddingでは、ツールがpin densityを認識しpaddingを自動設定することで、配線を行うための最適な配置を実現します。 - Unified Floorplan Constraint (UFC)

最先端プロセスで要求されるfloorplan制約をInnovus Implementation System独自のフォーマットで実現する新機能です。UFCフォーマットへのconvert、結果のcheck、違反箇所のfixと、一連の工程を全てサポートしています。

- 2.5D Padding

- Usability

Innovus Implementation System 18.1よりStylus Common UIが遂に正式プロダクト化されました。また新たなGUI機能により視認性が向上し、複雑化した設計を容易に行うことが可能となっています。

- Stylus Common UI

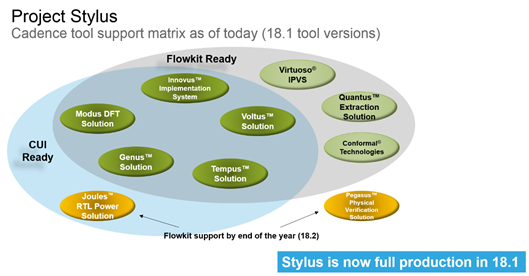

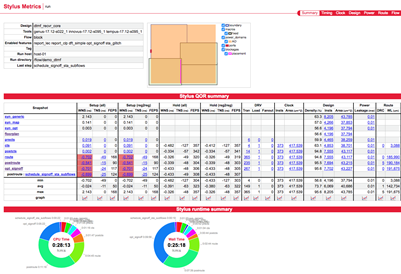

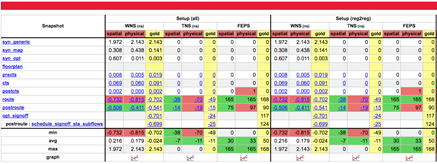

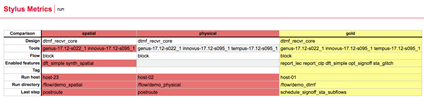

Cadenceのデジタル設計ソリューションである論理合成ツールGenus™ Synthesis SolutionからsignoffツールTempus™ Timing Signoff Solution、Voltus™ IC Power Integrity Solutionまでのfull flowを共通インターフェース化することで、シームレスな設計を実現しています。またmetrix機能も共通化されたことで、full flowを通してQoRの遷移や比較を容易に確認することが可能となっています。

図1:Stylus Common UI Full Flow のカバーエリア

図2:Stylus Common UI サンプル metrics1

図3:Stylus Common UI サンプル metrics2

図4:Stylus Common UI サンプル metrics3- 3D Layout GUI

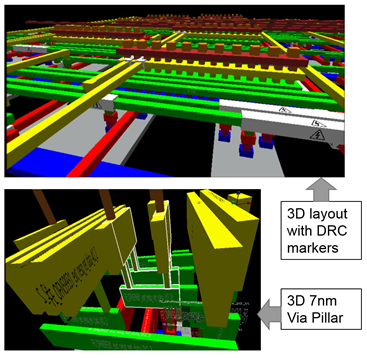

Innovus Implementation System のGUI上にて、full 3Dでのlayout描画を実現しました。3D Layout GUIを使用することで、先端プロセスで複雑化してきた配線構造も直感的に把握することが可能となっています。

図5:3D Layout GUI サンプルイメージ- TAT・PPA

Innovus Implementation System 18.1では従来の配置、配線、最適化などの各エンジンの高速化はもちろん、先端プロセス設計で重要となってくるdynamic powerの削減に着目した新機能を数多く搭載しています。

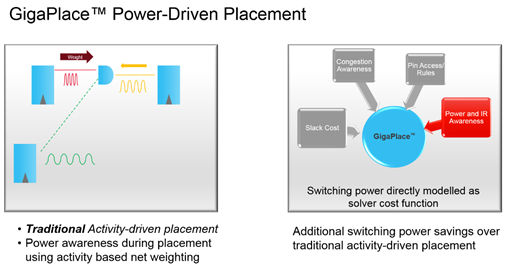

- Slack and Power Driven Placement (SPP)

従来のSlack Driven Placement (SKP)に、power activityを考慮させることが可能となりました。timingとpowerをコンカレントに最適化しながら、ベストな配置を実現いたします。

図6:Slack and Power Driven Placement(SPP)

- Timing and Power Driven Routing

DRC、timing、powerをコンカレントに最適化しながら配線を行うことが可能となりました。driver resistanceやjogの最小化、配線topologyをコントロールしながら配線を行うことで、高いpower削減効果が期待できます。 - Scan-independent Merging

従来ではscan chain接続を考慮してMBFF (Multi-Bit Flip-Flop)化を行っていたため、MBFF使用率が上がらないデザインもありましたが、新機能Scan-independent Mergingではscan chain接続に依存せず、同一scan group内でのMBFF化が可能となり、MBFF使用率を大きく上げることが可能となっています。 - FF Splitting @ PostCTS, PostRoute

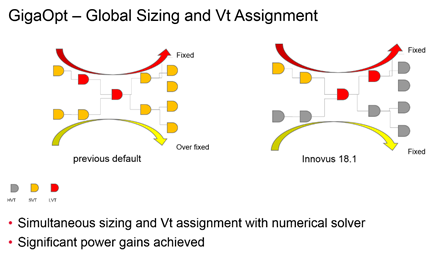

FFのsplitting機能もエンハンスされ、従来のPreCTSフェーズに加えて、新たにPostCTS、PostRouteフェーズでのFF splittingが可能となりました。設計収束に向けてより自由度の高い最適化が可能となり、設計収束期間の短縮が期待されます。 - Global Opt

従来のGlobal Optもアップデートされました。トレードオフとなるpowerとareaにとって最適なセル選択をパスベースで行うことが可能となり、より良いQoRを達成することが可能となっています。

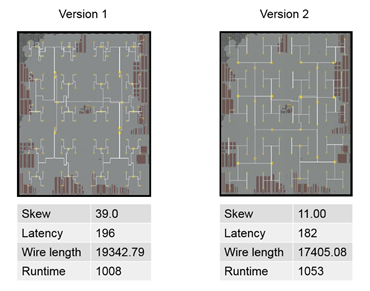

図7:GigaOpt - Flexible H-tree

アルゴリズムが刷新され、従来の結果に比べてclockの配線長とpowerが大きく改善しています。大規模でクロック構成が複雑なデザインに対しても、flexible H-treeを自動的にインプリすることが可能となっています。

図8:Flexible H-Treeサンプル結果比較 - Dual View ILM

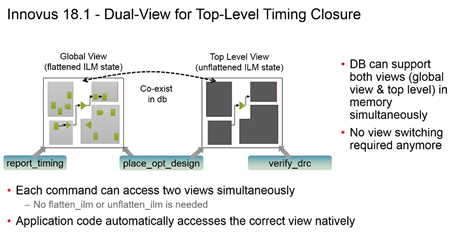

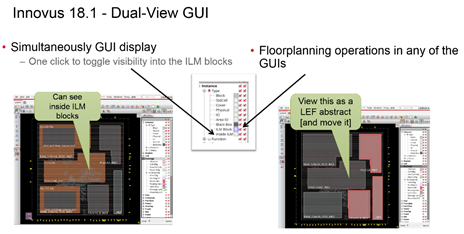

ILM (Interface Logic Model)の2つのView、Global View/Top Viewを同一メモリ内で持つようにデータベース構造がエンハンスされました。これによりILM化された階層blockのflatten/unflattenをシームレスに切り替えることが可能となり、階層設計時のTATが大幅に短縮されています。※本機能はInnovus Implementation System 18.11のβ機能になります。

図9:Dual View ILM

図10:Dual View ILM サンプルイメージ

- Slack and Power Driven Placement (SPP)

- Stylus Common UI

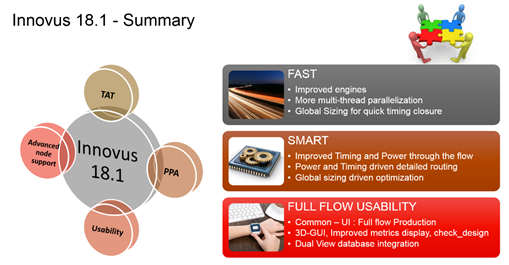

デジタルIC設計現場では様々な市場からの多種多様な要求により、高いPPA目標はもちろん、プロセス微細化による設計難易度の上昇や市場優位性を維持するためのスケジュール短縮等、常に数多くの課題に直面し続けています。ご紹介したように、Innovus Implementation System 18.1はそのようなユーザーの設計課題をクリアすることができる新機能を数多く搭載しています。更にここではご紹介できなかった新機能、アップデートもまだまだありますので、ご興味がございましたらCadence Online Support、もしくは担当AEまでお問い合わせください。

図11:Innovus Implementation System 18.1

フィールドエンジニアリング&サービス本部

デジタル&サインオフ

橘 克則

この記事に関する問い合せ先:

コーポレート・マーケティング部

E-mail:cdsj_info@cadence.com

Latest Issue

- ハイパフォーマンス・コンピューティングとコンシューマ機器に向けた次世代のメモリ規格DDR5に対応するケイデンスのIP

- CDNLive Japan 2018開催のご案内

- 編集後記

- Tempus-ECO ver.18.1最新機能のご紹介 ~ Multi-Level Clock Skewing ~

- ダミーフィルの影響をインデザインで解消 – Virtuoso IPVS SignOff Fill & Density Analysis

- 新時代の幕開け、アドバンストメソドロジ対応ツール Virtuoso ICADVM18.1

- アナログIC用信頼性考慮設計ソリューション「 Legato Reliability Solution 」

- 車載電子システム向け機能安全メソドロジ

- オートモーティブ電子システムデザイン・セミナー開催レポート

- 東アジアのお客様は英語の資料を要求してきましたよ

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues