ハイパフォーマンス・コンピューティングとコンシューマ機器に向けた次世代のメモリ規格DDR5に対応するケイデンスのIP

業界に先駆けて新しいDDRメモリ規格に対応するケイデンスのメモリIP

ケイデンスは2011年に旧デナリ社のDatabahnコントローラをIP製品のラインナップに加えて以来、つねに業界に先駆けて新しいDRAMメモリ規格に対応するコントローラIPとPHY IPを発表してきました。2011年、業界初のDDR4コントローラIPを発表し、翌年にはDDR4 PHYとコントローラを合わせて2400Mbpsの動作をシリコン実証しました。2013年には業界で初めてLPDDR4に対応するコントローラおよびPHY IPを当時業界最速の3200Mbpsでシリコン実証しました。続いて4266Mbpsで動作するLPDDR4 コントローラおよびPHY 、更に4266Mbpsで動作するLPDDR4X コントローラおよびPHYを業界で初めてシリコン実証しました。これらのシリコン実証を行う際には、IPを搭載したテストチップをDRAMメモリに接続して動作を評価し、DRAMメモリとのインターオペラビリティも確認しています。

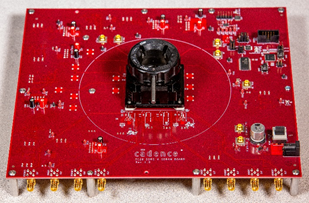

そしてこのたび5月にケイデンスはDDR5 IPを業界で初めてシリコン実証したことを発表しました。テストボードには、ケイデンスのDDR5コントローラおよびPHYを搭載したテストチップとMicron社より提供いただいたDDR5メモリのエンジニアリングサンプルが実装されています。DDR5規格は正式な仕様の策定と公開が今年後半となる見込みですが、ケイデンスはMicron社と共同で業界に先駆けてこの新規格への対応を示しました。

DDR5の普及とアプリケーション

今回DDR5のIPとDRAMメモリによるシリコン実証という重要な技術マイルストーンを達成できました。今後DDR5メモリはハイエンドサーバ、ストレージなどのエンタープライズアプリケーション、そしてコンシューマアプリケーションにおいて、DDR4メモリを徐々に置きえていくことでしょう。すでにハイエンドサーバ、ストレージなどのエンタープライズアプリケーションではDDR5メモリを使用するSoCの開発が始まっています。2022年頃には数量ベースでDDR5メモリがDDR4メモリを超えると予測されています。

DDR5メモリはDDR4メモリに対してメモリ容量が増え、データレートが更に高速化し、消費電力が低減されます。メモリ容量増加のためにDDR5メモリではDDR4メモリよりも微細化したプロセスを用いますが、一方メモリセルのデータリテンションは大容量化と微細化のために従来よりも厳しくなるため、DDR5ではon-die ECCを搭載します。

エンタープライズアプリケーションではDDR4 DIMMをDDR5 DIMMが置き換えられていくことでしょう。また昨今、DDRメモリとNAND Flashメモリを混載したNVDIMM-Pが考案されています。これはDRAMよりも価格が安く、大容量、待機時消費電力が低いNAND FlashメモリをDIMMに混載させることで、従来のDDRメモリだけのDIMMに対して低価格化、大容量化、低消費電力化を実現できるものです。このNVDIMM-PはDDR5メモリとNAND Flashメモリとの組み合わせで実現されることが予想されています。

その一方で、DRAMメモリ系のメモリとしてはDDR5に加えてGDDRメモリ、HBMメモリが登場していますが、DDR5メモリとこれら他のメモリはアプリケーションとその性能目標に応じて棲み分けられていくでしょう。HBMメモリとGDDRメモリはメモリバンド幅が重要視される高性能コンピューティング分野で用いられていますが、HBMメモリはインターポーザを含む製造コストをかけてもメモリバンド幅を最重要視するAIを含む高性能コンピューティング分野、GDDRメモリはメモリバンド幅も重要だが製造コストも下げたいアクセラレータやグラフィックカードで用いられています。

DDR5メモリはまずメモリ容量が最重要視されるエンタープライズサーバやエンタープライズストレージから普及が進んでいきます。そして普及が進むにつれてビット単価も徐々に下がり、コンシューマアプリケーションでもDDR4メモリを置き換えていくことでしょう。

DDR5 IPの評価とIPのプロセス展開

今回のDDR5テストボードは表面にDDR5 PHY IPとコントローラIPをシリコン化したテストチップソケット、裏面にMicron社製DDR5メモリを実装しています。

テストチップはTSMCの7nmプロセスを使用しており、従来のDDR4メモリの3200Mbpsに対して約1.4倍の4400Mbsで動作しています。今後ケイデンスはDDR5メモリを幅広いプロセスのSoCで使用できるように、12nm、16nm、および7nmから先端のプロセスに対してもDDR5 IPのポーティングを進めていきます。

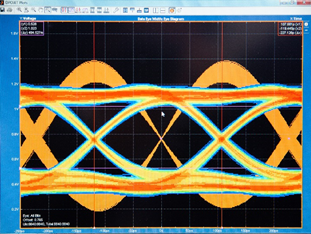

今回業界で初めて4400Mbpsのデータレートを実現していますが、Eyeダイアグラムはとてもきれいで十分なマージンがあることがみてとれます。このような動作特性を実現するにはIPの特性の向上だけでなく、パッケージやボードなどのシステム設計にも様々な配慮が必要です。ケイデンスではこれらのシステム設計にあたって実施したシミュレーションや知見をベースにシステム設計ガイド作成しお客様に提供しています。SoC開発者様では、シリコン実証済みのケイデンスのDDR5 PHYおよびコントローラIPと設計ガイドを使用してDDR5メモリサブシステムの開発を開始していただくことが可能となっています。

なおDDR5のテストボード評価のデモンストレーションが下記のウェブサイトで公開されていますので、ぜひご覧ください。

また7月20日(金)に開催されるCDNLive Japan 2018でもDDR5のテストボードを展示していますのでぜひお立ち寄りください

。

設計IP

伊原 誠

この記事に関する問い合せ先:

コーポレート・マーケティング部

E-mail:cdsj_info@cadence.com

Latest Issue

- CDNLive Japan 2018開催のご案内

- 編集後記

- Innovus 18.1: 待望のメジャー・アップデート、遂にリリース! ~業界をリードするデジタル設計ソリューションの新機能を搭載~

- Tempus-ECO ver.18.1最新機能のご紹介 ~ Multi-Level Clock Skewing ~

- ダミーフィルの影響をインデザインで解消 – Virtuoso IPVS SignOff Fill & Density Analysis

- 新時代の幕開け、アドバンストメソドロジ対応ツール Virtuoso ICADVM18.1

- アナログIC用信頼性考慮設計ソリューション「 Legato Reliability Solution 」

- 車載電子システム向け機能安全メソドロジ

- オートモーティブ電子システムデザイン・セミナー開催レポート

- 東アジアのお客様は英語の資料を要求してきましたよ

Archive

2023 Issues

2022 Issues

2021 Issues

2020 Issues