Overview

On-Device Accelerator Scalable Engine for Applications Ranging from Low-End (IP camera) to High-End (automotive, edge computing)

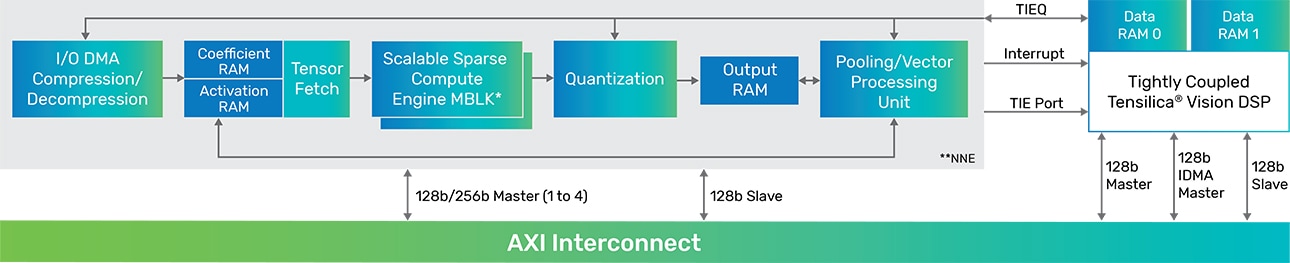

The Cadence® Tensilica® Deep Learning Neural Accelerator (DNA) engines are designed as offload accelerators that are paired with Tensilica DSPs for large performance and energy improvements. These standalone accelerators serve demanding and continuously growing artificial intelligence (AI) applications spanning the IoT, smart home, smartphones, AR/VR, drone, robotics, and automotive markets. DNA scalable/configurable accelerators can be configured to get best-in-class computational intensity and memory efficiency for various workloads, while DNA IP can be customized to map workloads to meet their power, performance, and area (PPA) and bandwidth constraints.

Key Benefits

Scalable Design to Adapt to Various AI Workloads

Configurable IP for scalable DL/AI workloads that can range from low (<1 terra ops per second (TOPS)) to very high compute (>10s of TOPS) needs

Efficient in Mapping State-of-the-Art DL/AI Workloads

Best-in-class performance for inferences per second with low latency and high throughput

End-to-End Software Toolchain and Simulator

GLOW-based Xtensa® Neural Network Compiler (XNNC) can optimize workload on DNA hardware accompanied by simulator to provide pre-silicon performance and metrics

True Random Sparsity Gain

Sparse compute engine exploits tensor sparsity (both weights and activations)

Industry-Leading Performance and Power Efficiency

High MAC utilization and TOPS/Watt combined with low energy consumption

Target Markets

Features

Products

Software Ecosystem

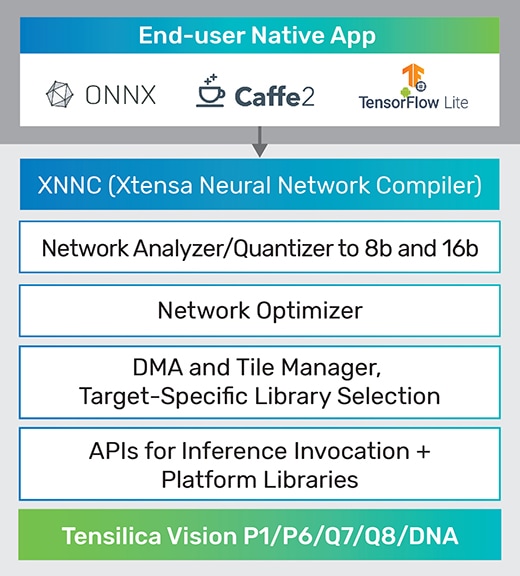

Xtensa Neural Network Compiler (XNNC)

Converts a floating-point convolutional neural network (CNN) into an optimized, fixed-point solution for Xtensa processors

- Ahead of time compiler toolchain

Can perform light pruning and compression to reduce computation, memory traffic, and storage needs

Can be used as command line tools and as a GUI that can be easily invoked in customer's software pipeline flow

- Programmable and extensible framework to adjust to scalable DNA hardware

- Flexible and future proof since compute layers change rapidly over time

- Supports mixed-precision data formats (8 bit/16 bit)

- Concurrency support by running more than on workload at the same time

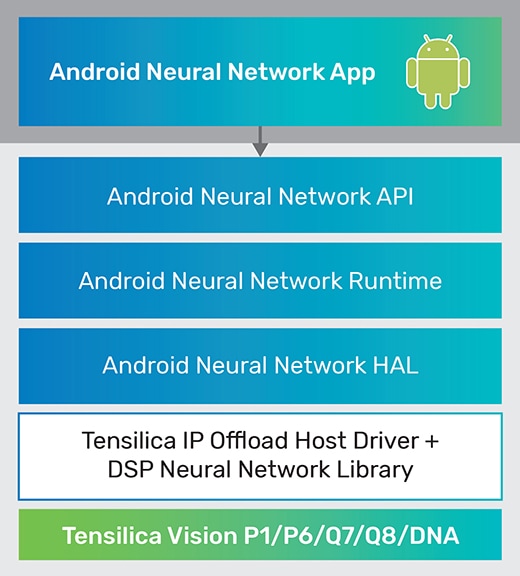

ANN

Android Neural Networks API (NNAPI) is an Android C API designed for running computationally intensive operations for machine learning on Android

- DNA can be interpreted as a back-end to NNAPI framework

- Android Neural Networks (ANN) provides dynamic optimized code generation for workloads

Partners

Cadence, through its Tensilica processor IP, brings together best-in-class products and services from industry leaders to help you accelerate the development of your SoC designs while meeting your demanding power and performance requirements. Browse the list of Tensilica processor IP service partners below.

Technologies

Functional Safety for Automotive

Cadence is committed to enabling Functional Safety applications across the Tensilica processor lineup, whether it's an off-the-shelf processor/DSP IP or a custom domain-specific processor for a specific application

Learn MoreTensilica Processor Technology

Differentiate, reduce time to market, add flexibility, and get the best performance, power, and area

Learn MoreTIE

Customize your DSPs/processors for optimized performance, energy efficiency, and differentiation

Learn MoreDevelopment Toolchain

Create a perfect match for your application, guaranteed correct by construction

Learn MoreTraining & Support

Need Help?

Cadence is committed to keeping design teams highly productive with a range of support offerings and processes designed to keep users focused on reducing time to market and achieving silicon success.

Free Software Evaluation

Try our SDK Software Development Toolkit for 15 days absolutely free. We want to show you how easy it is to use our Eclipse-based IDE.

Apply NowTraining

The Training Learning Maps link opens in new tab help you get a comprehensive visual overview of learning opportunities.

Training News - Subscribe link opens in new tab

Online Support

The Cadence Online Support (COS) system fields our entire library of accessible materials for self-study and step-by-step instruction.

Request SupportXtensa Processor Generator (XPG)

The Xtensa Processor Generator (XPG) is the heart of our technology - the patented cloud-based system that creates your correct-by-construction processor and all associated software, models, etc. (Login Required)

Launch XPGTechnical Forums

Find community on the technical forums to discuss and elaborate on your design ideas.

Find Answers