# Cadence Training Learning Maps

Cadence Training Services learning maps provide a comprehensive visual overview of the learning opportunities for Cadence customers. They provide recommended course flows as well as tool experience and knowledge levels to guide students through a complete learning plan. Learning Maps cover all Cadence<sup>®</sup> technologies and reference courses available worldwide. For course names, descriptions, and schedules, please select the Browse Catalog button at https://www.cadence.com/training.

#### Contents

- PCB Design and Analysis

- Custom IC, Analog, and RF Design

- Digital Design and Signoff

- System Design and Analysis

- IC Package Design and Analysis

cādence

• Tensilica<sup>®</sup> Processor IP

## PCB Design and Analysis Learning Map

Beginner

Advanced

|                                                                                                                                                                                                | Logic [                                                        | Design                                                      | PCB Design                                                                  | SI/PI Analysis                                                                       | Library Development                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------|

|                                                                                                                                                                                                | Allegro <sup>®</sup> Design Entry<br>HDL Front-to-Back<br>Flow | Allegro Design Entry<br>Using OrCAD <sup>®</sup><br>Capture | Allegro PCB Editor Basic<br>Techniques                                      | Essential High-Speed PCB<br>Design for Signal Integrity                              | Allegro PCB Librarian                                               |

| l                                                                                                                                                                                              | Allegro Design Entry<br>HDL<br>Basics                          | OrCAD CIS                                                   | Allegro PCB Editor<br>Intermediate Techniques                               | PCB Design at RF – Multi-<br>Gigabit Transmission, EMI<br>Control, and PCB Materials | Allegro EDM PCB Librarian                                           |

|                                                                                                                                                                                                | Allegro System (NEW)<br>Design Authoring                       | Allegro EDM Design<br>Entry HDL Front-to-<br>Back Flow      | Allegro PCB Router Basics                                                   | Allegro Sigrity <sup>™</sup> SI Foundations                                          | Allegro EDM for Administrators                                      |

|                                                                                                                                                                                                | Allegro System<br>Architect                                    | Allegro Team Design<br>Authoring                            | Allegro PCB Editor Advanced<br>Methodologies (NEW)                          | Allegro Sigrity PI                                                                   | Allegro EDM Administration for<br>OrCAD                             |

| l                                                                                                                                                                                              | Allegro Design Reuse                                           | Allegro EDM for<br>Engineers and<br>Designers               | Allegro High-Speed Constraint<br>Management                                 | Sigrity PowerDC <sup>™</sup> and<br>OptimizePI <sup>™</sup>                          | Allegro Design Entry HDL SKILL <sup>®</sup><br>Programming Language |

| k                                                                                                                                                                                              | Allegro AMS                                                    | Analog Simulation                                           | Allegro Update Training                                                     | Sigrity SystemSI <sup>™</sup> for<br>Parallel Bus and Serial Link<br>Analysis        | Allegro PCB Editor SKILL<br>Programming Language                    |

| H                                                                                                                                                                                              | Simulator                                                      | with PSpice <sup>®</sup>                                    | 1                                                                           | Model Generation and Analysis<br>using PowerSI, Broadband<br>SPICE and 3D-EM         | ý v v v v v v v v v v v v v v v v v v v                             |

|                                                                                                                                                                                                | Allegro AMS<br>Simulator<br>Advanced<br>Analysis               | Analog Simulation<br>with PSpice<br>Advanced<br>Analysis    | Advanced Design Verification<br>with the RAVEL Programming<br>Language •••• | Clarity 3D Solver                                                                    |                                                                     |

| New Course 🗰 Number of days for instructor-led course 🔲 🗵 GXL Tiers of Cadence products used in course 🔛 Online Course Available 😥 Digital Badge Available 💿 2020 Cadence Design Systems, Inc. |                                                                |                                                             |                                                                             |                                                                                      |                                                                     |

Advanced

#### IC Package Design and Analysis Learning Map

| IC Package Design                                                | SI/PI Analysis                                                            |  |

|------------------------------------------------------------------|---------------------------------------------------------------------------|--|

| SiP Layout                                                       | Allegro Sigrity <sup>™</sup> SI Foundations                               |  |

| 4                                                                | 2                                                                         |  |

| Allegro® Package Designer                                        | Allegro Sigrity PI                                                        |  |

| 4                                                                | 1                                                                         |  |

| Allegro FPGA System Planner                                      | Sigrity PowerDC <sup>™</sup> and OptimizePI <sup>™</sup>                  |  |

| 2                                                                | 🥺 🗂 🛄                                                                     |  |

| Allegro Sigrity Package Assessment and Model Extraction          | Sigrity SystemSI <sup>™</sup> for Parallel Bus and Serial Link Analysis < |  |

| 1                                                                | 3                                                                         |  |

| OrbitIO <sup>™</sup> System Planner                              | Model Generation and Analysis using PowerSI, Broadband SPICE, and 3D-EM   |  |

| 1                                                                | 2                                                                         |  |

| Advanced Design Verification with the RAVEL Programming Language | Clarity 3D Solver                                                         |  |

| 2                                                                | 1                                                                         |  |

Beginner

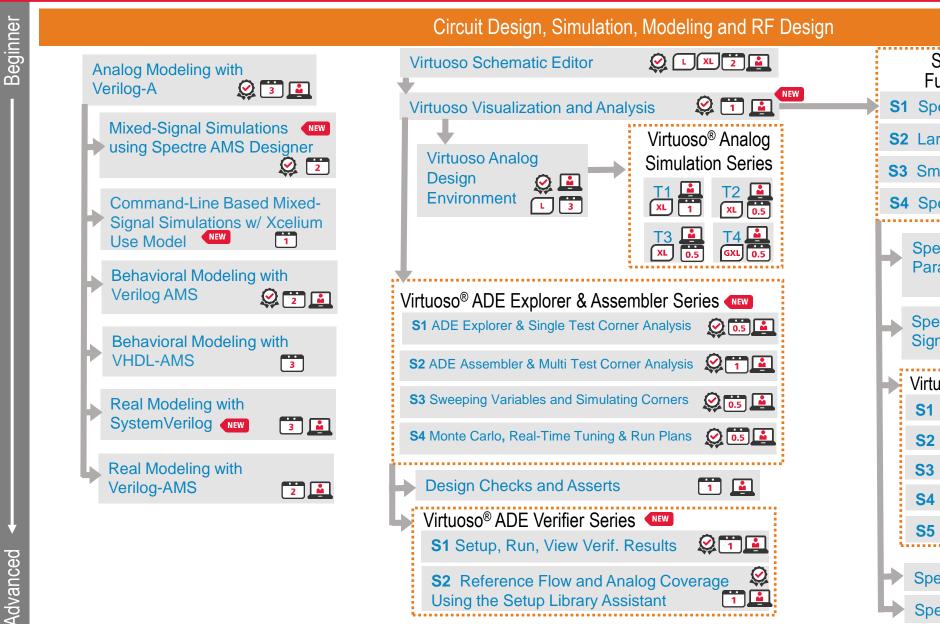

## Custom IC, Analog and RF Design Learning Map

1 of 2 – see next page

Advanced

2

**#** Number of days for instructor-led course New Course

💶 😰 😥 🔝 🔝 🔝 🔝 🖬 🔝 🔝 🔝 Iters of Cadence products used in course 📓 Online Course Available 😥 Digital Badge Available 🛛 🖾 2020 Cadence Design Systems, Inc.

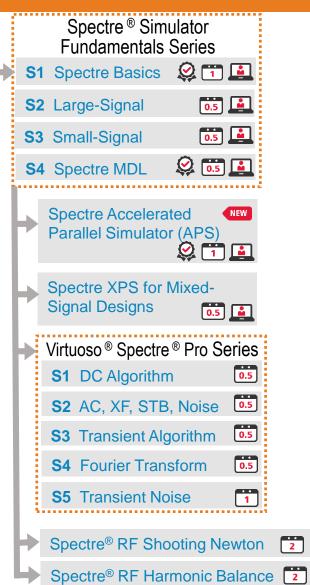

#### Custom IC, Analog and RF Design Learning Map

#### 2 of 2 – see prior page

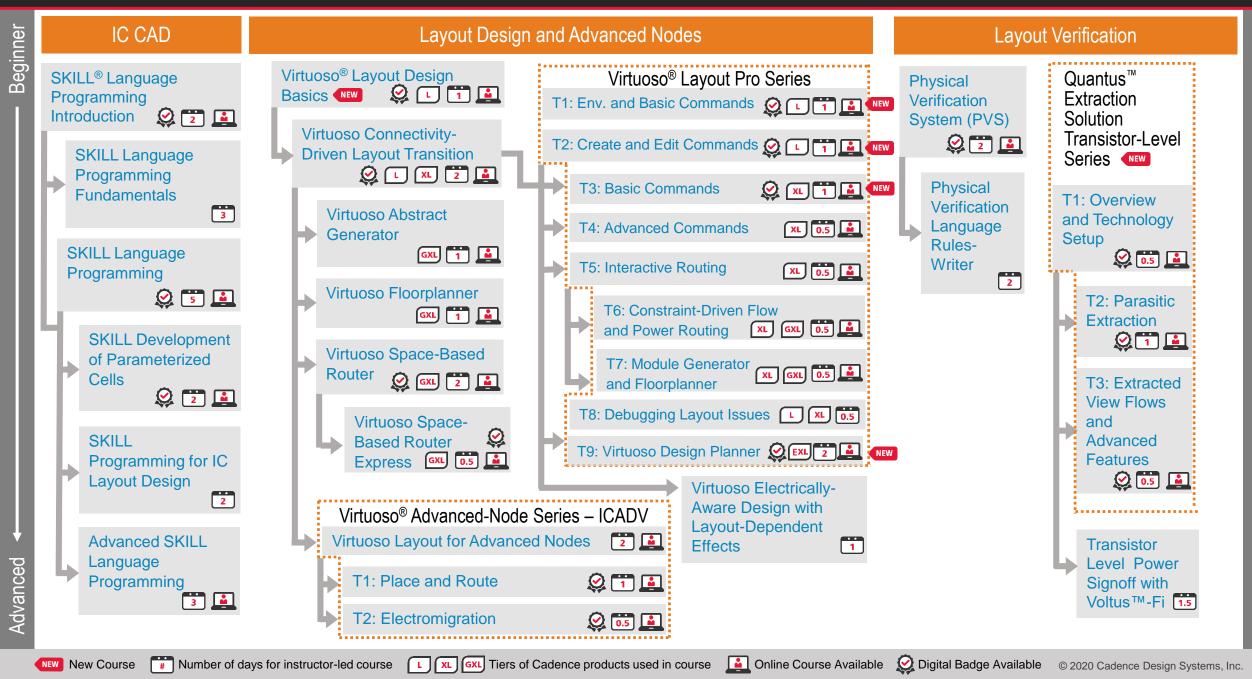

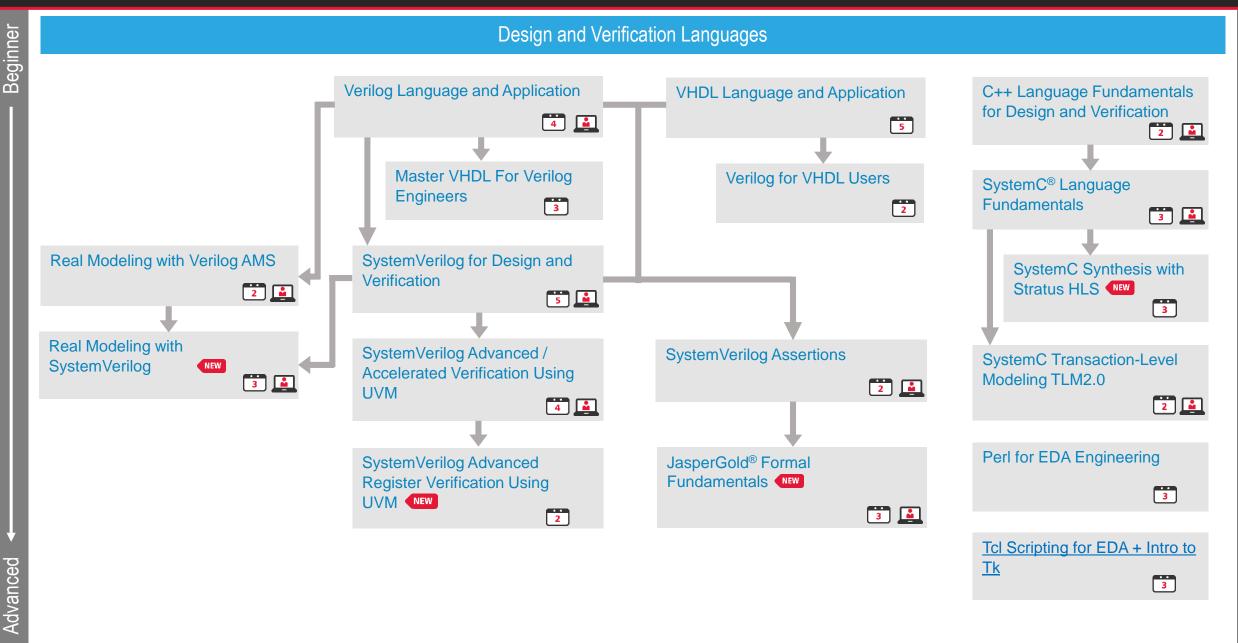

### Digital Design and Signoff Learning Map

Digital Badge Available

Online Course Available

New Course

Wumber of days for instructor-led course

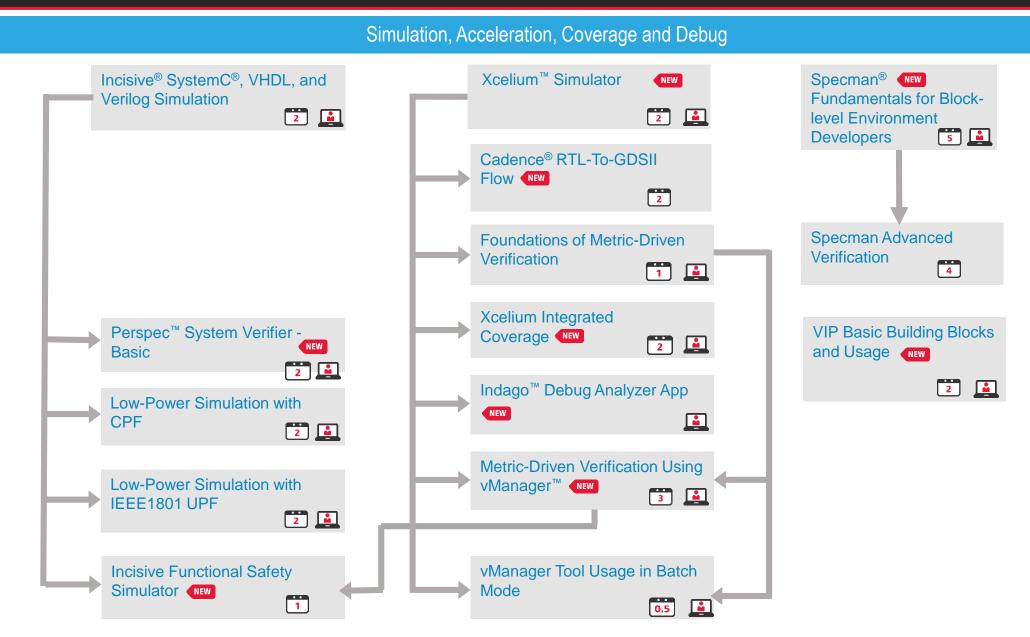

#### System Design and Verification Learning Map

Advanced

New Course

#### System Design and Verification Learning Map

New Course

© 2020 Cadence Design Systems, Inc.

Advanced

Wumber of days for instructor-led course L GXL Tiers of Cadence products used in course Online Course Available

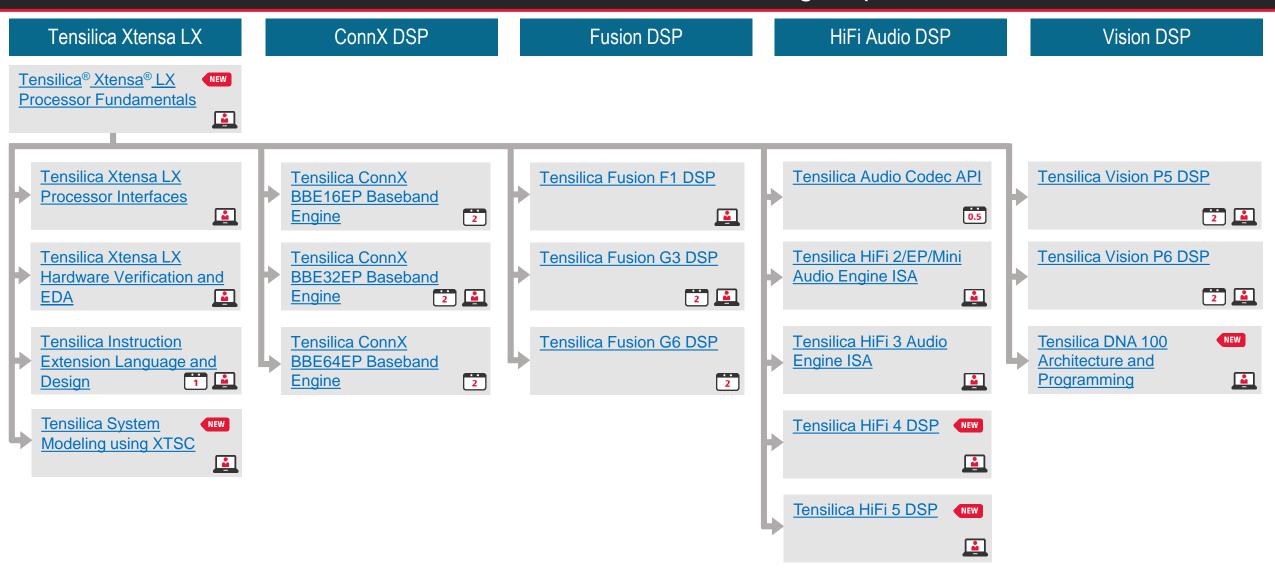

#### **Tensilica Processor IP Learning Map**

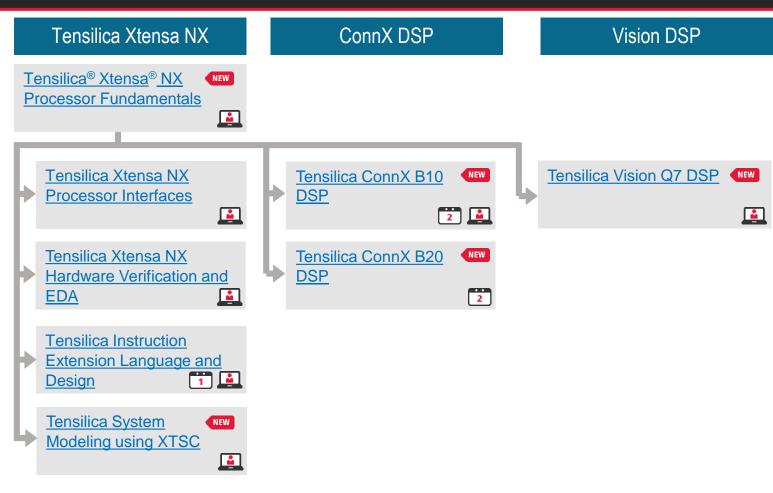

#### Tensilica Processor IP Learning Map

2 of 2 – see prior page

# cadence

© 2020 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <u>www.cadence.com/go/trademarks</u> are trademarks or registered trademarks of Systems, Inc. Accellera and System Care trademarks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or trademarks or service marks owned by MIPI Alliance. All PCI-SIG specifications are registered trademarks or trademarks or trademarks are the property of their respective owners.